主题中讨论的其他器件:HALCOGEN

您好、

我们开始使用 TMS570LS1114ZWT、过去我们使用的是 TMS570LS0914PGE。

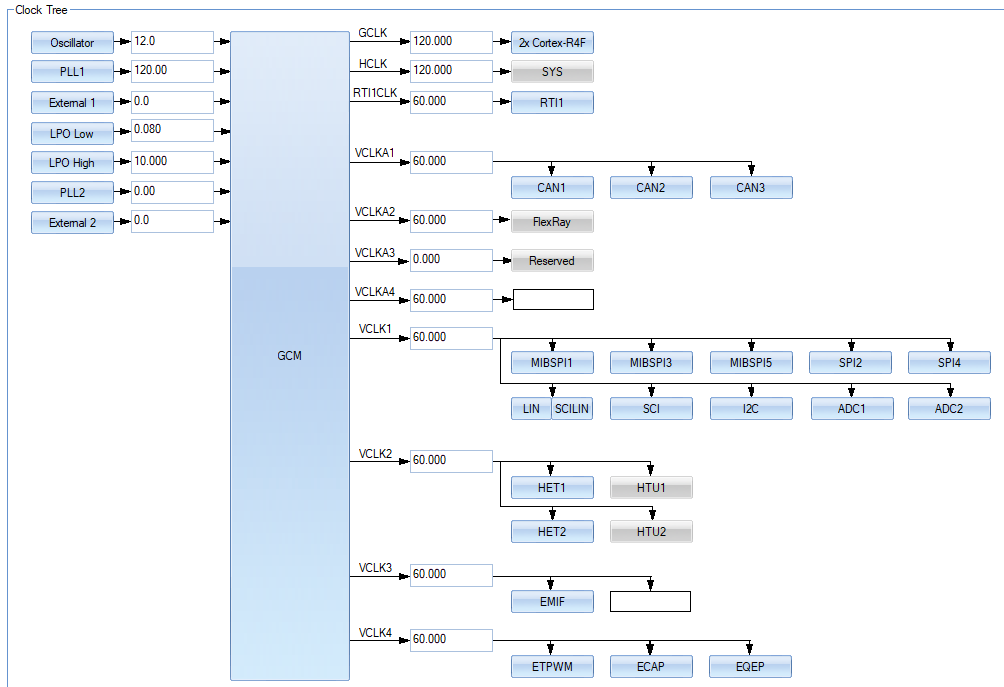

我们的振荡器具有12MHz。 我们使用示波器验证了这一点。

通过 Halcogen、我们生成了一个初始项目。 我们尝试将内核频率设置为120MHz (以及160MHz 和180MHz)。 但是、我们在旧项目中使用此120MHz。 我们的配置如下。

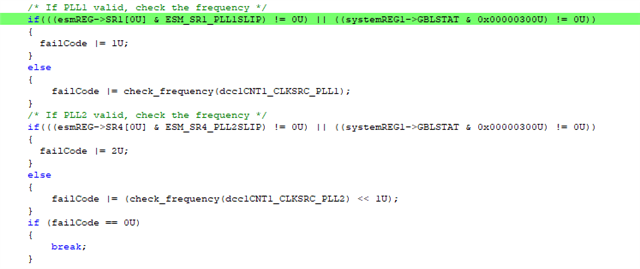

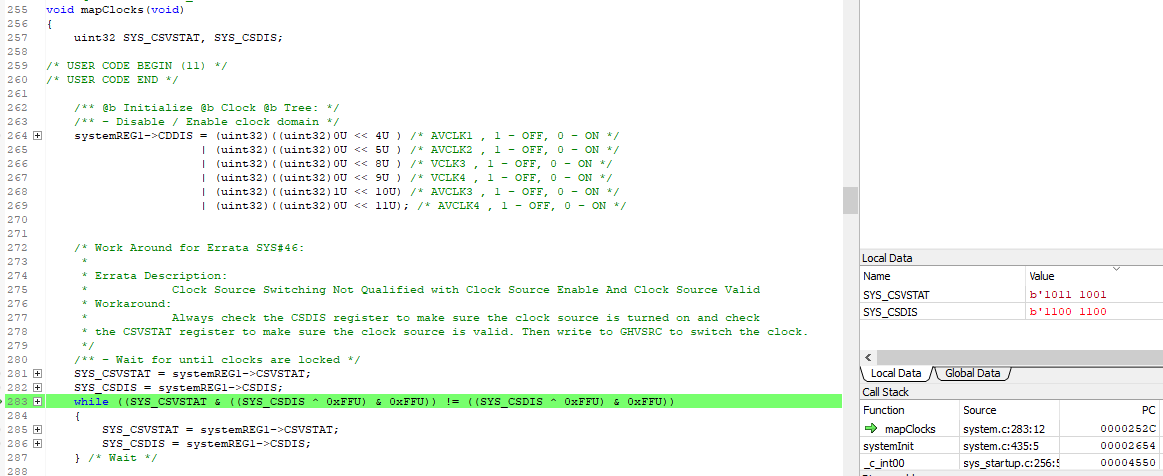

代码时、我们将会看到它。 它在程序等待直到时钟被锁定时堆栈。

您是否知道我们如何检查硬件设计是否正确? 是否需要测量一些点?

或者、我们如何验证 halcogen 中没有缺失的配置设置?

以下是我的配置:

此致、

Thorben