主题中讨论的其他器件: HALCOGEN

您好!

我们正在使用贵公司的 TMS570LS3137开发产品。 在最近的软件版本中、芯片报告了 ESM 组1通道6事件错误。

查找手册发现这意味着闪存 ECC 发现了一个单位可纠正的错误。

我们的应用场景不允许出现此错误、即使该错误是可纠正的。

我的问题有以下三点:

1.此错误的原因是什么?

除了硬件故障之外、哪些软件操作会导致闪存 ECC 错误?

TMS570的 MPU 模块可以防止意外的闪存写入操作。 由于重写闪存被阻止、为什么 ECC 检查失败?

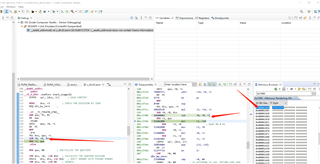

2.我们如何跟踪这个问题?

3.我不理解技术参考手册中 FCOR_ERR_ADD 寄存器的位[2:0]的含义以及 FCOR_ERR_POSbits[7:0]的描述。 例如、您能详细解释一下吗?

期待您的回复、谢谢!