主题中讨论的其他器件: HALCOGEN

你好。

我已经通过 EMIF 连接了一个 SDRAM。

现在、我已经尝试了一些存储器配置、如果对 SDRAM 的未对齐写入工作正常(始终启用 MPU):

对于"严格排序"和"器件"配置、不能进行未对齐写入。

对于"可高速缓冲"、可以进行一个不带定位的写入。

此外、如果 MPU 被禁用、则不能进行未对齐写入。

但哪种存储器配置是正确的?

谢谢、BR

Christian

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好。

我已经通过 EMIF 连接了一个 SDRAM。

现在、我已经尝试了一些存储器配置、如果对 SDRAM 的未对齐写入工作正常(始终启用 MPU):

对于"严格排序"和"器件"配置、不能进行未对齐写入。

对于"可高速缓冲"、可以进行一个不带定位的写入。

此外、如果 MPU 被禁用、则不能进行未对齐写入。

但哪种存储器配置是正确的?

谢谢、BR

Christian

从 ARM 文档中可以清楚地看出、只有 Normal Memory 类型 属性支持未对齐的访问。

Cortex-R4和 Cortex-R4F 技术参考手册中 AXI 访问对存储器系统的影响 包含:

[引用]但是、器件和严格排序的存储器始终不可高速缓存。 此外、对器件或严格排序存储器的任何未对齐访问都会生成对齐故障、因此不会导致任何 AXI 传输。 这意味着本章给出的访问示例绝不会显示对器件或严格排序存储器的未对齐访问。

ARM v7-M 架构参考手册(ARM DDI 0403E.d)中的 A3.4.5正常存储器部分包含:

[引用]正常存储器功能强大、这意味着它具有以下属性:

•可以支持未对齐的访问。[/QUERP]

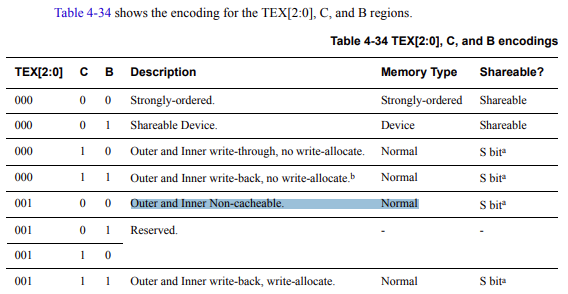

由于 TMS570LS3137没有高速缓存、因此认为 EMIF 的 MPU 区域访问控制需要根据 Cortex-R4和 Cortex-R4F 技术参考手册中的以下内容将 TEX[2:0]、C 和 B 编码配置为"外部和内部不可高速缓存"和"正常":

我尚未将上述设置跟踪到 HALCoGen GUI 配置选项。

考虑到通过 EMIF 访问内部 RAM 和 SDRAM 的 ARM 定义都是有效的、那么就正常存储器而言、是。

我了解了为 RM48L952ZWT (具有 EMIF 的基于 Cortex-R4F 的器件)创建的 HALCoGen 项目。

在项目初始化时创建的默认 MPU 设置中:

a.在 HALCoGen R4-MPU-MPU 选项卡中、覆盖内部 RAM 的 MPU 区3具有一种"normal_OINC_Nonshared"(存储器类型 NORMAL 外部和内部不可连接和不共享)。

b.覆盖 EMIF SDRAM 的 MPU 区6在 HALGoGen R4-MPU-MPU 选项卡中有一种类型为"严格有序的可共享存储器"(存储器类型为严格排序的可共享存储器)。

通过查看 sys_MPU.asm 来查看使用的 MPU 区访问控制寄存器设置、并基于 Cortex-R4F TRM 中的信息:

| 键入 HALCoGen MPU 配置 | MPU 区访问控制寄存器值(由 SYS_MPU.asm 设置) | TEX | S | C | B | 说明 | 存储器类型 | 可共享? |

| NORMAL OINC_NONSHARED | 0x0308 | b001 | 0 | 0 | 0 | 外部和内部不可高速缓存 | 正常 | 非共享 |

| 严格排序_可共享 | 0x0300 | b000 | 0 | 0 | 0 | 严格排序 | 严格排序 | 共享 |

基于上述内容、如果要使用 EMIF SDRAM 区域来允许未对齐访问、则 应在 HALCoGen MPU 配置中选择 NORMAL OINC_NONSHARED 类型。