请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TM4C129DNCZAD 您好!

我有一位客户使用 TM4C129进行设计、他们使用 TM4C 作为 SSI 从站、主站使用自己的晶体/振荡器计时。 即使时钟最终略高于10MHz、由于振荡器或 PLL 漂移/抖动而导致的频率轻微变化是否存在任何问题?

Munan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我有一位客户使用 TM4C129进行设计、他们使用 TM4C 作为 SSI 从站、主站使用自己的晶体/振荡器计时。 即使时钟最终略高于10MHz、由于振荡器或 PLL 漂移/抖动而导致的频率轻微变化是否存在任何问题?

Munan

您好!

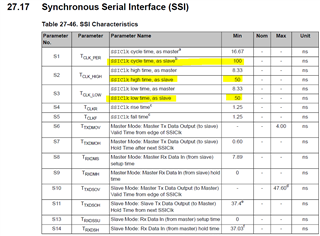

我认为这不是问题。 请确保数据表中显示的时序参数符合从模式的要求。

注:SYSCLK 或 ALTCLK 用作 SSInClk 的源、具体取决于 CS 域的设置

SSI 时钟配置寄存器(SSICC)中的配置。 对于传统主机模式、

使用时、SYSCLK 或 ALTCLK 必须至少比 SSInClk 快两倍

SSInClk 不能超过60MHz 的限制。 SYSCLK 或 ALTCLK

必须至少比 SSInClk 快12倍。 在从器件传统模式下为最大值

SSInClk 的频率为10MHz。