主题中讨论的其他器件:HALCOGEN

您好!

这与我之前的问题有关: e2e.ti.com/.../982659

对于我们的项目、我们有一个要求、即我们应该禁用未使用的外设。 我通过为 PSPWRDWNSETx 和 PCSPWRDWNSETx 寄存器中未使用的外设写入适当的位来禁用时钟和存储器、如上面的主题所述。

为了验证时钟信号的翻转实际上会禁用未使用的外设、我还为 MibSPI3禁用了时钟信号、MibSPI3在我们的应用中用于总线主控配置。 我的期望是在 MibSPI3的输出数据线路上没有任何活动。

但是、当我对 MibSPI3进行写操作时、我仍然可以看到数据输出在 MOSI 线路上、并且 CLK 信号也存在、并且似乎与从器件的通信仍在工作。 这是预期行为吗? 我希望禁用该外设的时钟和存储器会将其关闭、对其进行写入将不起作用、尤其是在外部引脚上。

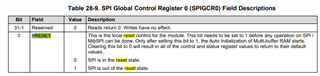

这是 pcrREG3->PSPWRDWNSET0寄存器的内容、我的理解是在该寄存器中、将4-8位置位以禁用 PS[1]位、该位是与 MibSPI3相关的位。

我正在向 PSPWRDWNSET0写入(0xF << 4)(除其他外)、这会导致值0x5出现在 PSPWRDWNSET0的 PS[1]字段中。 我认为这是可以的、因为 TRM 中有一条注释说"只有在相应位位置具有从器件的位才会被实现。 写入未执行的位无效、读取为0。" 我认为未实现未设置位。

我还通过写入 PCSPWRDWNSET0寄存器位来禁用 MibSPI3 RAM。

我不确定这是否重要、但我们的初始化过程首先通过 将 FFs 写入 PSPRWRDWNCLRx 寄存器来启用所有时钟、然后在不同的位置禁用我们不使用的模块。

谢谢、此致、

Bartek