大家好、团队、

我的客户使用具有外部16MHz 振荡器和120MHz 系统时钟的器件。

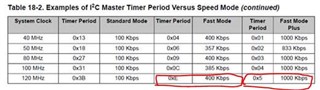

客户使用快速模式(400kbps)和快速模式增强版(1000kbps) I2C。

客户测量了 I2C 信号的时钟频率、但他们观察到的是快速模式下为387kHz、超快速模式下为922kHz。

您能告诉我在这些条件下的典型(或目标) SCL 频率吗?

如果还提供其变体数据、那将会有所帮助。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

我的客户使用具有外部16MHz 振荡器和120MHz 系统时钟的器件。

客户使用快速模式(400kbps)和快速模式增强版(1000kbps) I2C。

客户测量了 I2C 信号的时钟频率、但他们观察到的是快速模式下为387kHz、超快速模式下为922kHz。

您能告诉我在这些条件下的典型(或目标) SCL 频率吗?

如果还提供其变体数据、那将会有所帮助。

此致、

首先、您没有提到客户是在主模式还是从模式下使用 I2C。 假设 TM4C1294是主器件、SCL 频率将与时钟源一样准确。 使用一个外部16MHz 晶振应该会使它非常精确。 那么、以下是我认为您的客户可能测量不同频率的可能原因。

1) 1) PLL 配置不正确、系统时钟不是120MHz (我认为这种情况不太可能、但应该仔细检查)

2) 2)从器件正在进行时钟扩展

3) 3)客户正在使用频率计或示波器的频率功能测量 SCL 时钟。 I2C 时钟是不连续的、并且在两次传输之间可能保持高电平。 这会导致测量的平均时钟速率低于每个位的时钟速率。 让客户在传输过程中测量位的时钟周期并计算周期中的频率。

您好、Bob-San、

感谢您的评论。

>首先,您没有提到客户是在主模式还是从模式下使用 I2C。

很抱歉、缺少信息。 客户使用 TM4C1294作为主设备、正如您所设想的那样。

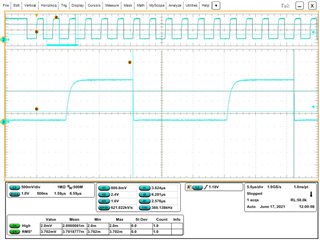

我从客户那里得到波形。 有关快速模式 SCL、请参阅下面的附件。

我不认为(2)从器件的时钟拉伸或(3)测量方法是频率差异的原因。

关于(1) PLL 配置、客户观察到 SPI 时钟(TM4C1294是主器件)的频率符合预期。 因此系统时钟似乎配置正确。 客户将确认这一点、以防万一。

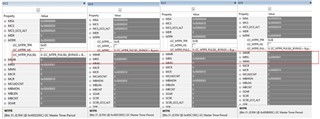

我让客户确认 I2C 毛刺脉冲滤波器设置、但 MTPR 寄存器的脉冲配置为零。

如果你能提出其他可能的理由,我将不胜感激。

此致、

如果不是时钟拉伸、而不是测量技术、则很可能是配置问题或晶体问题。 您提到它们使用的是外部16MHz 晶体。 它们能否测量外部晶体的频率? 应在连接到 OSC1引脚89的一侧测量该值。

他们如何配置 PLL? 是:

g_ui32SysClock = SysCtlClockFreqSet((SYSCTL_XTAL_16MHZ |

SYSCTL_OSC_MAIN |

SYSCTL_USE_PLL |

SYSCTL_CFG_VCO_240), 120000000);

此示例仅对 TivaWare 版本2.2.0.295有效。 如果他们不使用此版本、他们使用的是哪个版本?

我不能说这是原始意图的一部分。 确实、它会延长低电平时间、以缩短时钟的上升时间。 时钟拉伸电路的设计固有的特性是、它将在高电平周期内保持对时钟的计数、直到在 SCL 引脚上看到高电平。 它无法判断从 SCL 开漏驱动器关断到 SCL 引脚上的电平变为高电平之间的延迟是由电阻器-电容器延迟引起的、还是由主动将 SCL 线路保持在低电平的从器件引起的。

[引用 userid="109338" URL"~/support/microcontrollers/other-microcontrollers-group/other/f/other-microcontrollers-forum/1011700/tm4c1294kcpdt-i2c-scl-frequency/3758875 #3758875"]您是否有参考信息,说明上升时间会延长多长时间的时钟低电平周期?它是上拉电阻器强度、SCL 网络上的电容和 SCL 引脚的 VIH 阈值这三个方面的函数。 该阈值将介于0.5V 和2.4V 之间、通常接近1.5V、但会随工艺、温度和电源电压的变化而变化。

您好、Bob-San、

如您所述、客户观察到 SCL 频率随上拉电阻器一起变化。

| 上拉电阻器[欧姆] | 470 | 1.1k | 2.4k | 4.7K |

| 周期时间[us] | 1.034 | 1.052 | 1.084 | 1.138. |

| 频率[kHz] | 967.118 | 950.5703 | 922.5092 | 878.7346 |

| 高电平时间[ns] | 436 | 450 | 484 | 546 |

| 低电平时间[ns] | 591. | 591. | 591. | 590 |

| 上升时间[ns] (1.14V~2.14V) |

6.4. | 17. | 36. | 80 |

客户看到 SCL 低电平周期是固定的、高电平周期随上拉电阻器一起变化、而您说低电平周期将发生变化。

在器件的时钟拉伸过程中、客户观察结果是否正确?

此致、

是的、这是由上拉电阻器的上升时间引起的时钟拉伸。 我将其称为拉伸的低电平周期、因为器件中的主 I2C 电路会将其视为低电平周期、直到 SCL 线路上升到 VIH。 在这种情况下、上升时间实际上随着上拉电阻的增加而延长。 主器件将 SCL 保持为低电平的时间是恒定的。 SCL 在再次变为低电平之前高于 VIH 的时间是恒定的。 SCL 释放到达到 VIH 之间的时间是增加的时间。