Thread 中讨论的其他器件:EK-TM4C1294XL、

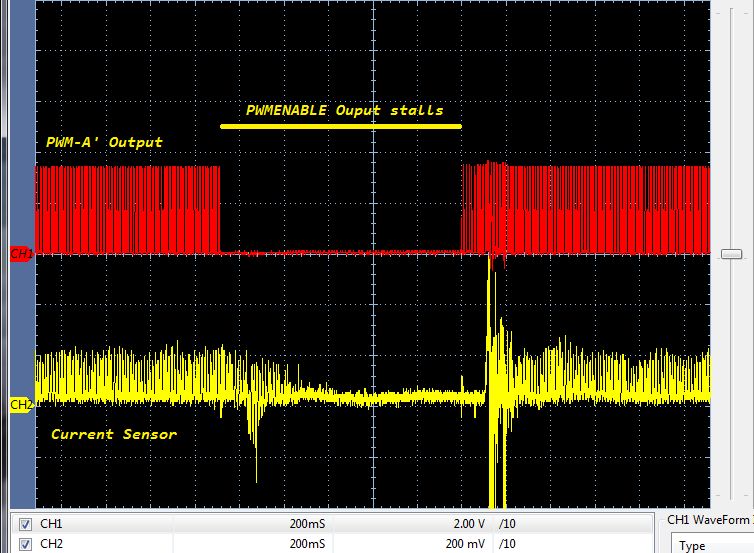

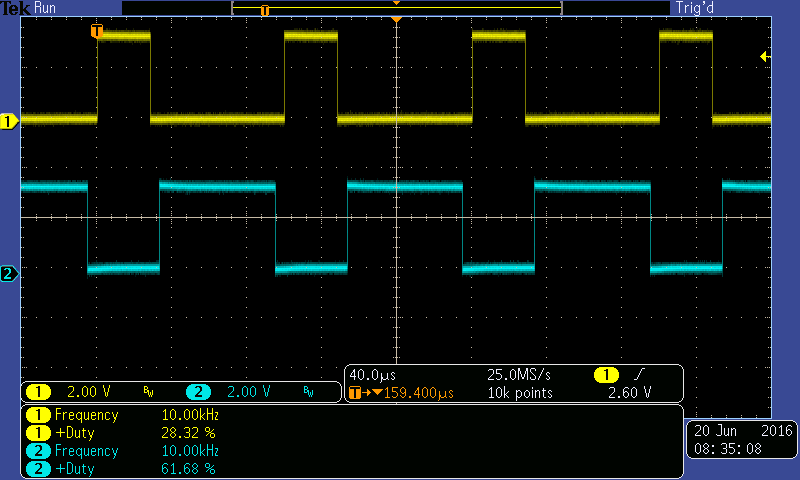

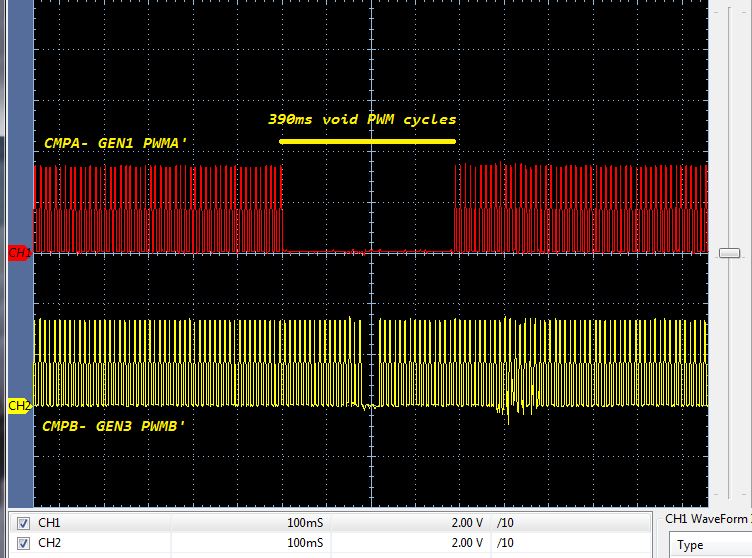

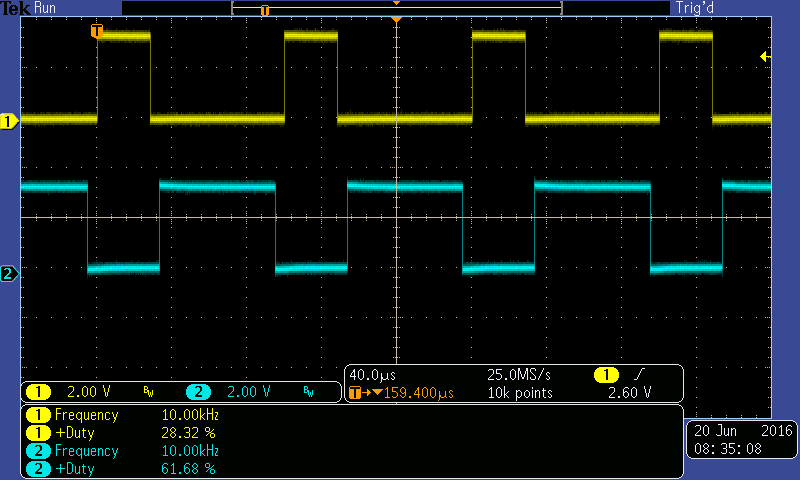

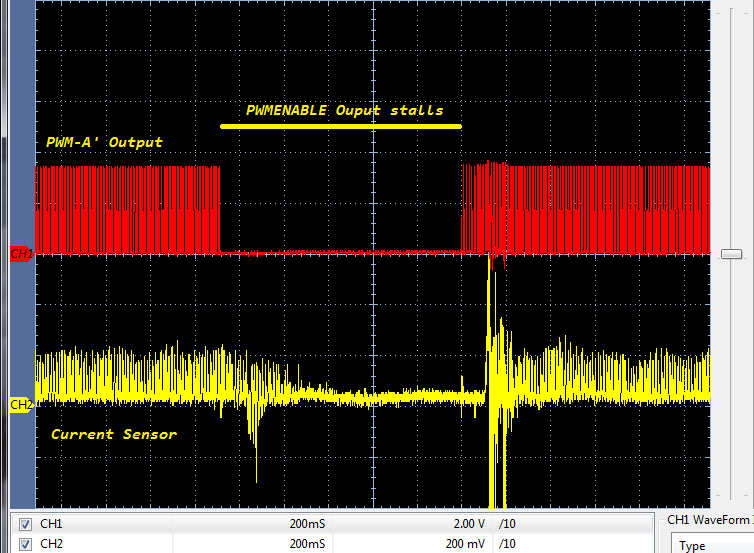

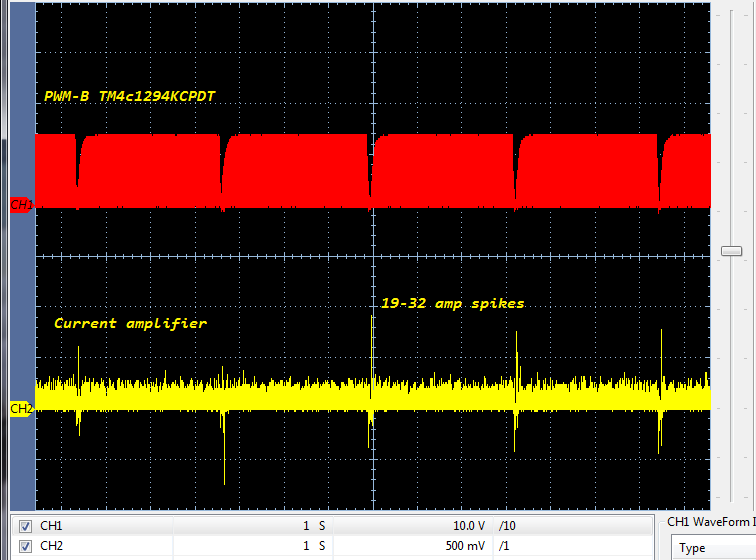

之前曾发布过类似的问题、即在间隔1-5秒之间什么会导致 PWM 再次发生电气干扰。 然而、1/2电桥输出驱动器在大多数时间都非常干净、而在所有 PWM 周期中突然发生100ms 至200ms 的崩溃。 我怎么能如此盲目地不去看这场电风暴,除了灾难性的事情。

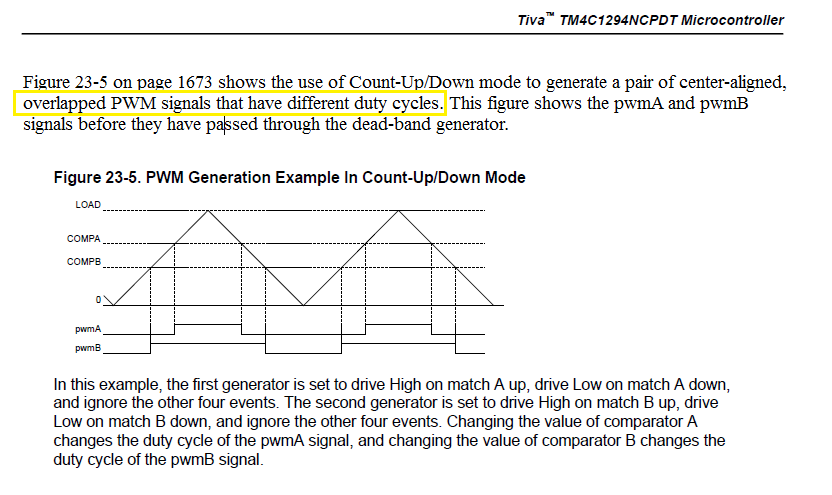

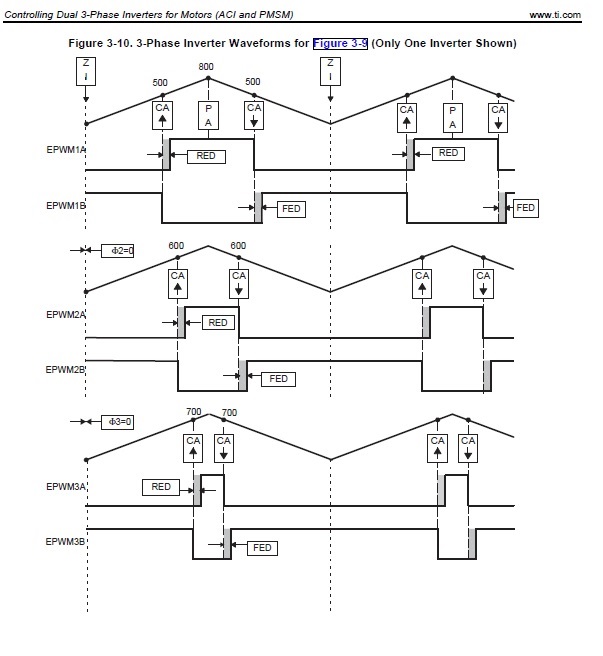

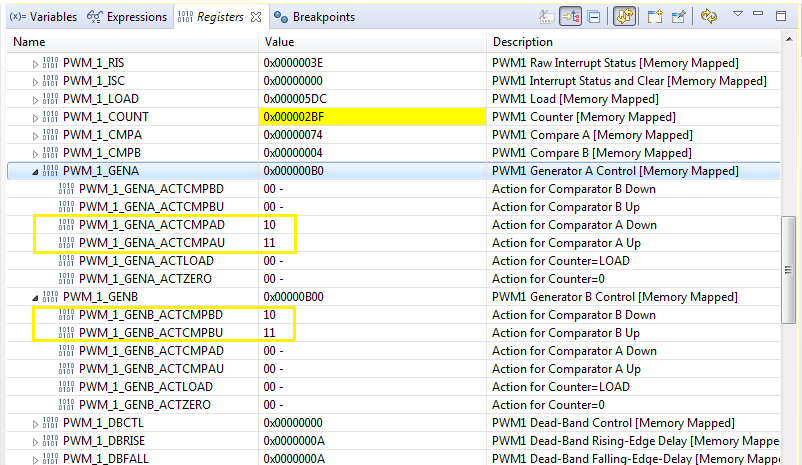

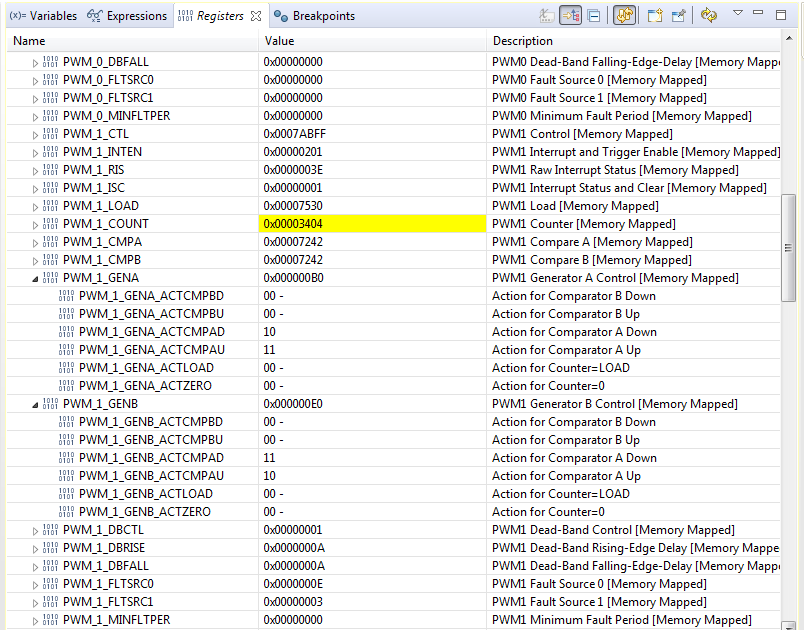

最近我发现、在 GPTM 驱动的输出间隔 PWMENABLE 寄存器期间、全局同步更新可能不同步。 因此、在加载发生器计数期间启用 PWM 输出可能并非所有条件中的最佳状态。 奇怪的是、这种频繁的随机风暴不会使直流逆变器崩溃、但绝对会严重破坏发生的 EMF 尖峰对硬件的影响。 有点像割草、在这种情况下、草地更深、必须更用力地推入才能穿过粗糙的路面。 出口时、您会突然加速、然后甚至超出自走速度。 从那以后购买了42英寸甲板式割草机、但这是另一个庭院故事。

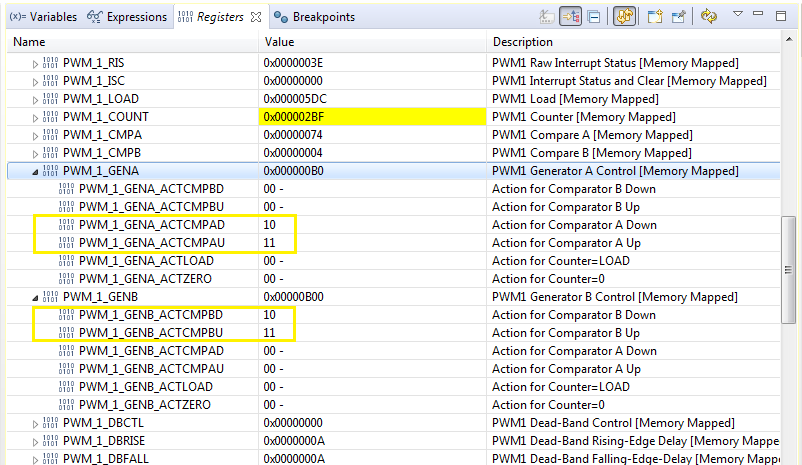

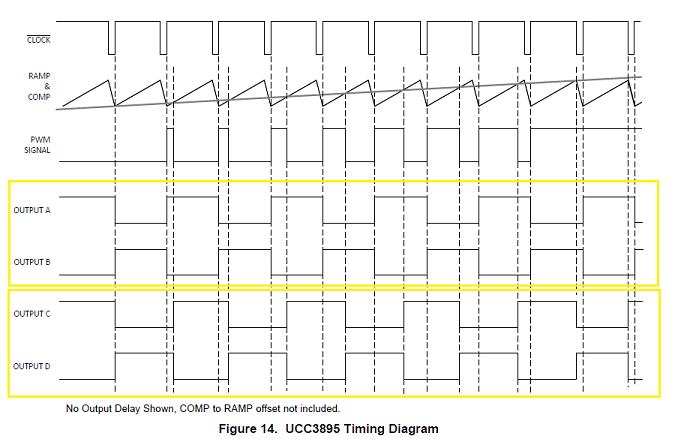

无论如何、GPTM 配置的 OSHT 具有一个中断处理程序函数、用于控制 PWMENABLE、并在 ADC 中断处理程序内的2个 PWM 周期内重新加载 OSHT 计数。

然后还有另一个 GPTM 用于捕获 ADC 中断的边沿时间、用于确定通过另一个 NVIC 中断 PWMENABLE 驱动换向的新 PWM 边沿。

在全局同步更新期间、也许会发生 PWM (过载)、ADC 中断通过 OSHT 超时间接控制外部换向功能环路。

问题是如何在不增加复杂性和/或中断 PWM 换向周期的情况下停止过度运行?

我的第一个猜测是添加一个 while not loop 到驱动换向事件的 OSHT 处理程序中、这是不是要回避?

是否有人曾看到过同样的随机 PWM 电风暴?