请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS570LC4357 在这里发布、希望它能帮助其他人。 花了几天时间尝试弄清为什么 SPI 时钟极性0和相位0 (我将其称为模式0)不能按预期工作。

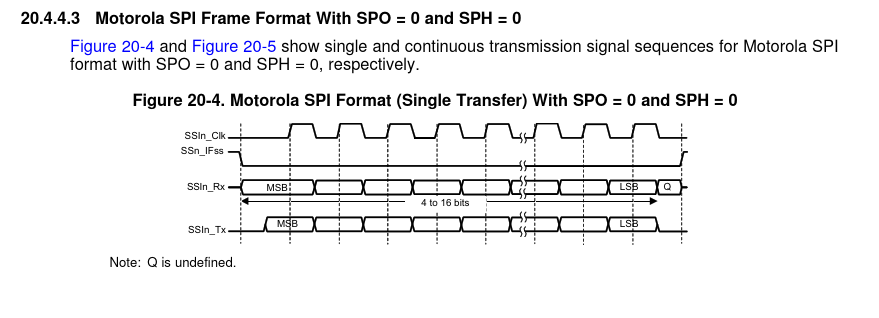

下面是大多数人期望模式0 (CPOL=0、CPHA=0)看起来像的一个示例、来自 TI CC26x0 TRM:

在此时序图中、SSIn_Rx 可能更适合称为 MISO、而 SSIn_Tx 则称为 MOSI。

TMS570 SPI 实现(mibSPI)似乎对0相应该是什么有一个奇怪的想法。 以下是与 TMS570LC4357相同的图:

显然、这在与"标准"模式0 SPI 外设通信时不会非常可靠地工作。 您可能需要将相位更改为1:

希望这能帮助别人!