您好!

我的客户正在使用 EPI Hostbus 16位模式。 当它们写入时、CS 信号和 WRn 信号同时下降。 但是 、当它们读取时、 RDN 信号在一个周期 CS 下降后下降。 这是正常的吗? 我要做些什么来确保没有延迟?

下面是用于 设置 EPI 的代码:

EPImodeSet (EPI0_BASE、EPI_MODE_HB16);

EPIDividerSet (EPI0_BASE、0x1);

EPIConfigHB16CSSet (EPI0_BASE,0)( EPI_HB16_MODE_ADMUX |

EPI_HB16_CSCFG_ALE_SINGLE_CS |

// EPI_HB16_CSCFG_ALE_Quad_CS |

EPI_HB16_BURST_交通 |

EPI_HB16_WRWAIT_3 |

EP_HB16_RDWAIT_3 |

// EPI_HB16_MODE_FIFO |

EPI_HB16_WORD_ACCESS |

// EPI_HB16_CSCFG_ALE_DUAL_CS |

EPI_HB16_CSBAUD |

EPI_HB16_CLOCK _GATE _IDLE |

EPI_HB16_BSEL));

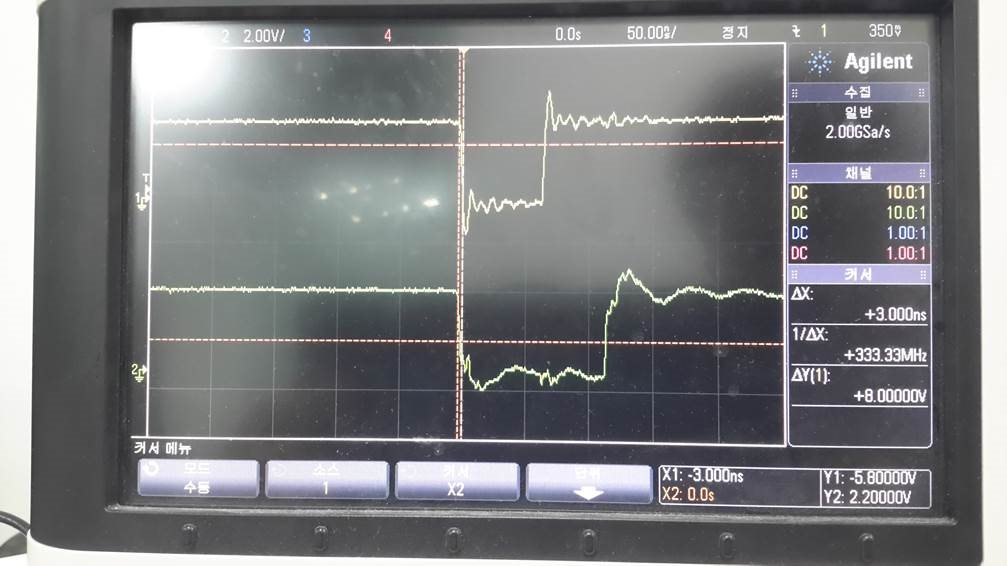

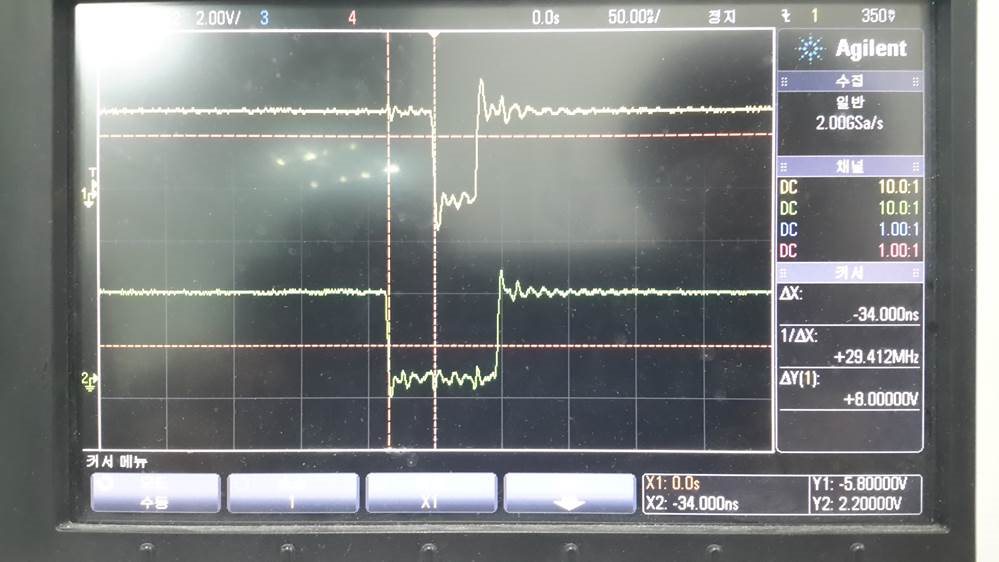

这些是用于写入 和 读取的时序图

写入(WRn -黄色、CS -绿色)

读取(RDN -黄色、CS -绿色)

此致、

TED