[引用 user="Daniel Vamos"]我有基于时钟函数的代码(ADC 相关内容),但我在 RTOS 包中找不到任何计时器示例

Daniel、您好!

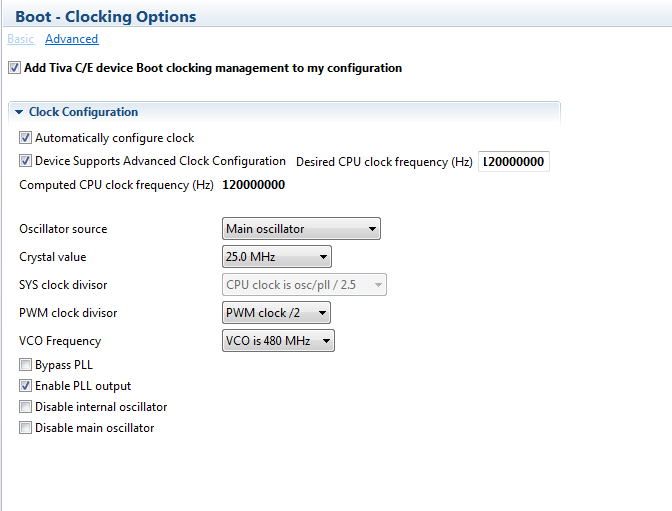

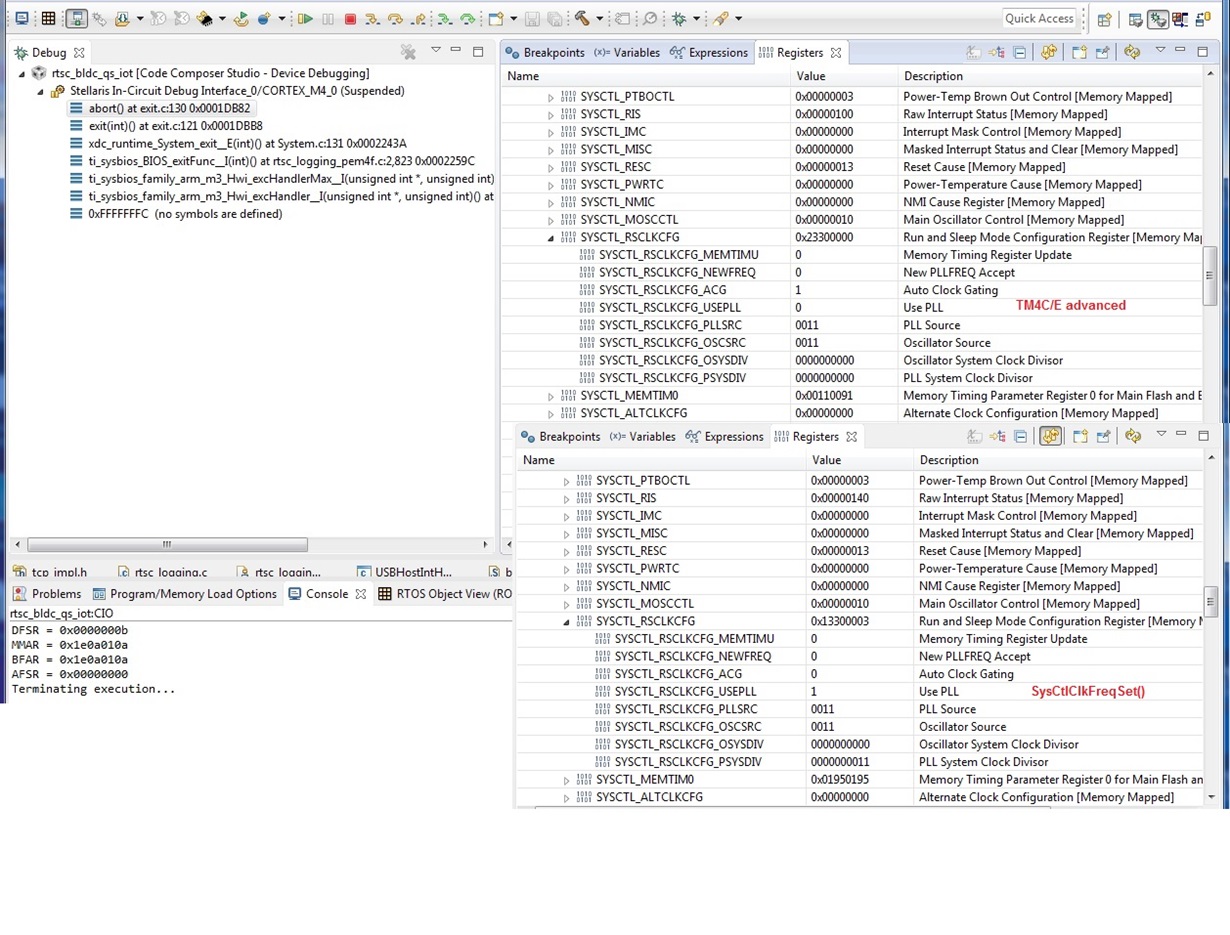

我们有几个 ADC 序列发生器采样率@2MSPS、需要 为 SYSCLK 120MHz 正确配置 PLL 分频值。 尽管如此、很遗憾、最新的 TI-RTOS 启动模块未能实现任何此类目标。 事实上、为了 使用 TivaCtlSysClkFreqSet()来实现适当的 ADC 时钟速度、启动模块中的 TivaC/E 高级计时被禁用。 奇怪的是、ROV Boot 显示 输出 PLL=false、但 ADC 和 EMAC PHY 以正确的时钟 速度运行。 在 POR 之后、我们无法单独获取 RTOS TM4C 高级时钟来执行应用程序而不会快速产生故障。 在发生故障之前、应用程序似乎以缓慢的运动执行。

无论 将 PSYSDIV (SYSDIV) 作为典型设置进行2或2.5、在引导模块 TM4C 高级时钟从 PIOSC 转换到 MOSC 中的效果都不好。

祝你好运。