请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM2434 客户询问他们应该在数据表中遵循哪种设计指南。

我们是否需要控制 QSPI 的 LBCLK 和 DQS 长度?

他们计划使用 S25HS512TFANNHI013 (与 EVM 相同,1.8V 版本)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

客户询问他们应该在数据表中遵循哪种设计指南。

我们是否需要控制 QSPI 的 LBCLK 和 DQS 长度?

他们计划使用 S25HS512TFANNHI013 (与 EVM 相同,1.8V 版本)

您好、Lawrence、

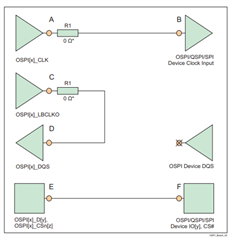

[引用 userid="13437" URL"~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1167441/am2434-spi-flash-layout-guideline ]客户询问他们应在数据表中遵循哪种设计指南。 [/报价]这取决于它们的用例是什么。 如果他们计划在50MHz 以上运行 QSPI、则应考虑使用 外部板环回 设计实现

QSPI 不使用来自闪存器件的 DQS 信号、而是将 SoC 上的 DQS 引脚用作外部环回输入。 它的功能是 在更高的速度下实现更轻松的时序闭合。

[引用 userid="13437" URL"~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1167441/am2434-spi-flash-layout-guideline "]我们是否需要控制 QSPI 的 LBCLK 和 DQS 长度?[/quot]在 LBCLK 和 DQS 传播时需要注意以下事项:

"OSPI[x]_LBCLKO 引脚到 OSPI[x]_DQS 引脚的信号传播延迟(C 到 D)必须大约是 OSPI[x]_CLK 引脚到连接的 OSPI/QSPI/SPI 器件 CLK 引脚(A 到 B)的传播延迟的两倍"

有关 设计和实现的更多信息、请参阅器件数据表9.2.3 OSPI/QSPI/SPI 电路板设计和布局指南下的第9.2.3.2节"外部电路板环回"

最棒的

Daniel