你(们)好。

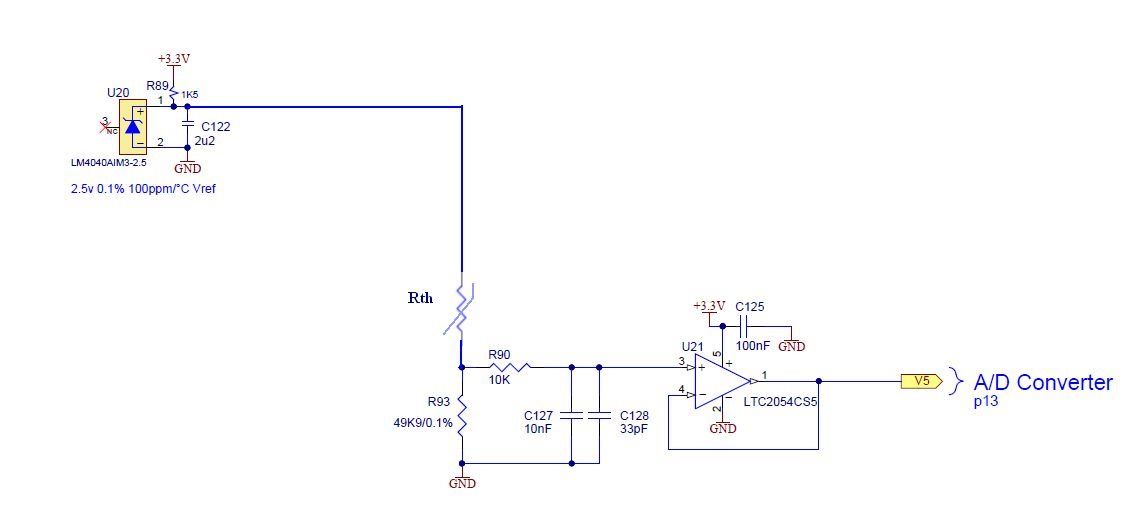

该 TM4C129X MCU 的内部 ADC 通过分压器(具有热敏电阻)对缓冲电压进行采样、具体如下所示。

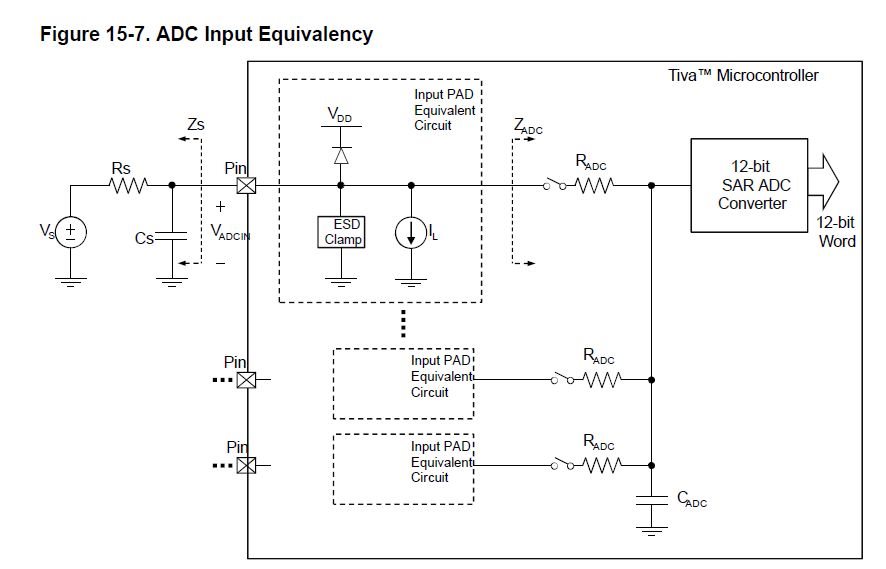

我发现12位 ADC 的误差约为 2-3%(可能 是80个计数?)。 我不能容忍超过0.2%的误差或8个误差计数。 我已经展示过、只需用 DMM 设置探测 ADC 输入引脚即可测量我获得正确 ADC 值的电压、否则它将关断2-3%。 我假设 DMM 在引脚上放置一个容性负载、在下面的 ADC 输入等效原理图中充当 CS。 正如我仿真的那样、DMM 的10M 输入阻抗不是通过在 ADC 引脚上插入一个10M Ω 电阻器到 GND 而消除误差的10M Ω 输入阻抗。

数据表 显示、任何 ADC 引脚的外部源极电阻的最高值为 Rs<=500欧姆(@1MSPS)。 未给出 Rs 的最小值、因此我认为我是一个聪明的设计人员、通过以配置单位增益(电压跟随器)的运算放大器(LTC2054)的形式输入极低的源电阻-请参阅上面的电路图。

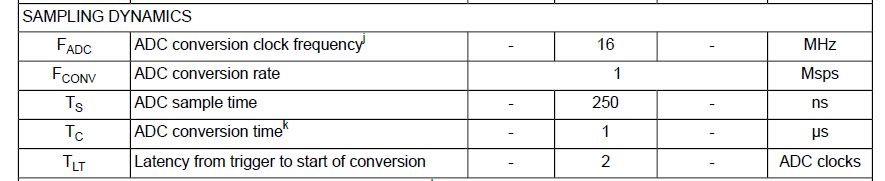

我认为这个输入电路导致了误差、因为运算放大器的稳定时间(对于12位 ADC 为0.01%)远长于 (大约几十 us) 250ns (@1MSPS)的 ADC 采样时间

此后、我已经阅读了大量有关 SAR ADC 输入信号调节的文献[1]、并建议在运算放大器之后使用 RC 滤波器进行 BW 限制、并在采样电容器充电时最大限度地降低不稳定。 我把这个 RC 滤波器放在运算放大器之前! 对于 BW 限制而言是可以的、但由于运算放大器对 SAR ADC 采样电容器进行充电、因此对限制不稳定没有好处。 我还没有尝试在运算放大器之后插入这些外部 R 和 C 组件、如果从设计更改的角度来看、会有一些影响。

通过将 ADC 的采样时间延长到100us 而不是250ns、我是否有另一种方法可以在固件而非硬件中解决此问题?? 我在数据表中看不到这样做的选项、 只需要调整采样保持窗口时间"ADC 模块提供了通过 ADC 采样序列 n 采样保持时间(ADCSSTSHn)寄存器对序列中每个步进的采样保持窗口进行编程的功能。" (第1058页)

这是数据表中的 ADC 输入电路。 我的 Rs (运算放大器的输出电阻)非常低(可能为几欧姆)、而我的 Cs 可能仅为寄生轨道电容的几 pF。

[1] 《优化 SAR ADC 设计》、作者:TI 的 Bonnie Baker、 《适用于 SAR ADC 的输入驱动电路》 、《使用 TMS320F28xx/28xxx DSC 设计模拟接口的概述》