团队、

我有一位客户遇到了以下问题:

"我们的多款产品上都有 TivaTM4C129ENCPDT 微控制器。 我们刚刚购买了以太网测试套件 Sifos PVA 3002。

我们运行了3个 Tiva 板、并在全部3个板上查看抖动和噪声测试中的错误。 我已经运行了笔记本电脑和路由器、但没有将其视为常见错误或设置错误。

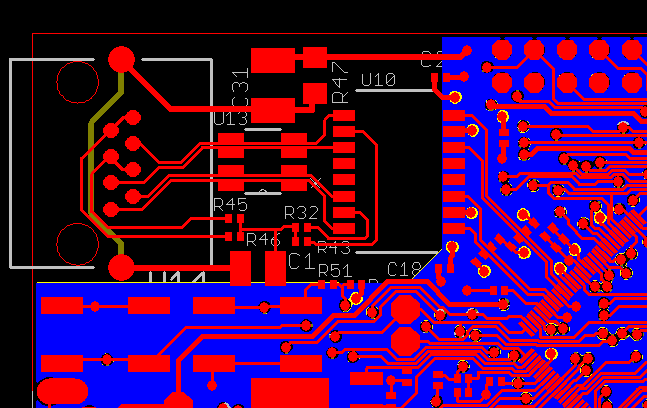

3个电路板采用3种不同的布局、但基本上采用相同的设计。 我已经做了一些接地、时钟等方面的实验、无法做出任何改进。 对于使用内部 PHY 的 Tiva、这是正常的吗? SW 人员说、他使用几个月前的 Tiva 源代码。 没有过时的东西 我在勘误表中没有看到任何提及。"

您能评论一下这种情况的潜在原因吗? 他们还向我发送了原理图和读出了他们的报告,但我不想在这里分享。 如果需要、团队的一名成员可以脱机与我联系。