主题中讨论的其他器件:TM4C1294NCPDT、 INA240

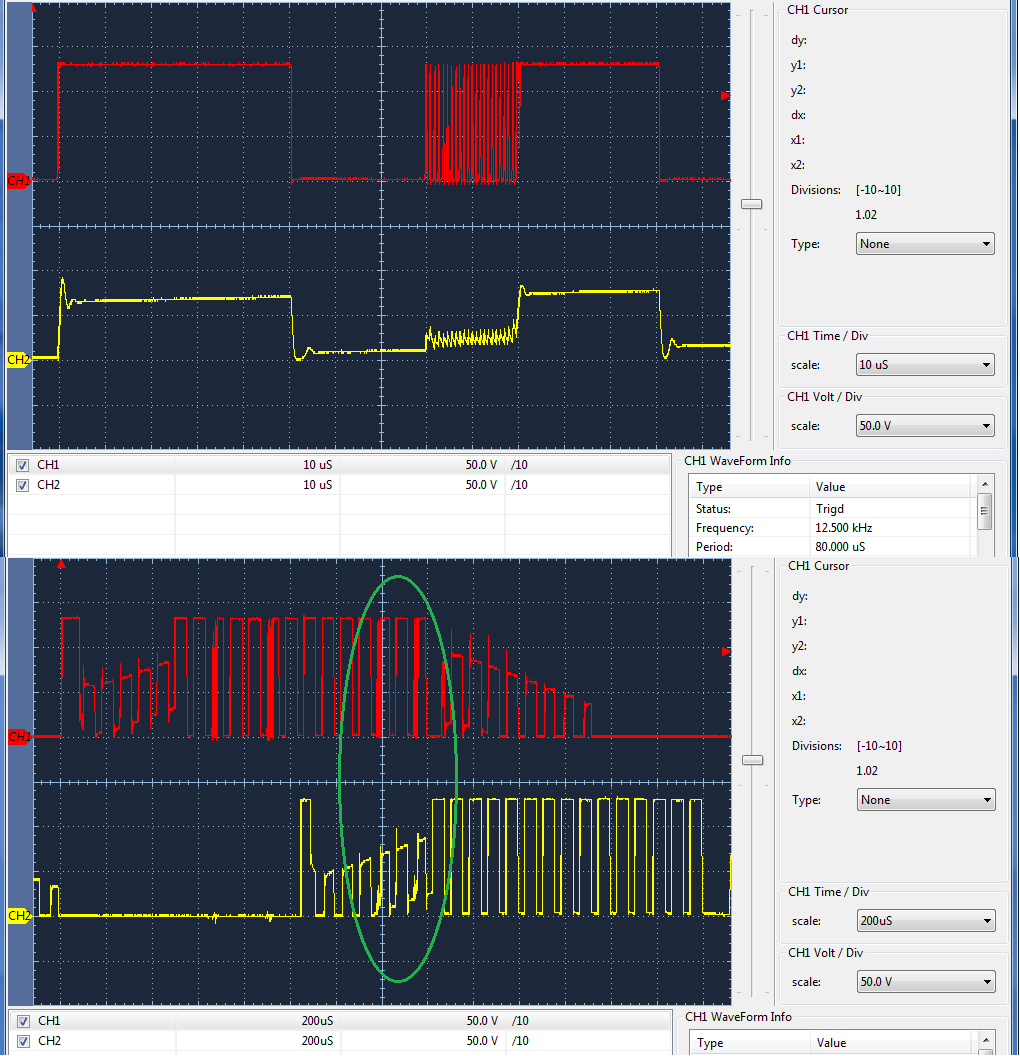

3个 PWM 发生器1、2、3、但只有 2个调制 80us 周期、其中有源占空比 为50us 导通时间( 高脉冲)、其中240ns 斩波脉冲 存在于 50us 导通时间的前32us 中。 其他发生器1、3永远不 会产生 类似的斩波脉冲、但会在 产生的三相 逆变器波形中改变活动导通时间的上升/下降沿。 通过 对 PWM 发生器做出反应的三相1/2桥栅极驱动器可以明显看到发生器2的斩波脉冲。 否则、在 单个发生器边沿时间内很难想象240ns 斩波脉冲。

可能 是因为它 需要 2个 PWM 发生器协同工作来产生 适当的栅极驱动 模式、从而 生成 DSP 梯形 波形、而不会发生1/2电桥击穿。

所有三个 PWM 发生器 在计数达到 零时通过发生器1的中断进行全局同步更新。 以下命令 指示3个发生器在 新计数加载到 发生器1中断处理程序内的每个发生器后执行全局同步更新。

我 认为 在全局 同步更新之前加载了类似计数的所有3个发生器应该生成 几乎 相同的240ns 斩波脉冲、这是不对的?

ROM_PWMSyncUpdate (PWM0_BASE、 (PWM_GEN_1_BIT|PWM_GEN_2_BIT|PWM_GEN_3_BIT);