Thread 中讨论的其他器件:SysConfig

您好!

我是否知道:

1、我是否知道如果我仅使用 core0、我是否可以选择任何人的实例?

2、由于我想使用 TI 寄存器 ISR、intr_num 与实例的映射是什么?

在此示例中、

AM263x 中的 GPIO 引脚:

AM263x 具有139个 GPIO 引脚

该器件具有四个 GPIO 模块实例、每个 R5FSS 处理器内核有一个专用实例

- Pinmux/IOMUX 允许使用4:1 MUX 将 GPO 引脚控制分配给特定的 R5FSS 处理器内核 (MCUSDK SysConfig 自动生成用于配置此功能的代码)

- 所有处理器内核都可以观察到 GPI 引脚

GPIO 模块最多能够支持144个专用引脚。 AM263x 实现了139引脚。

AM263x 中的 GPIO 中断:

关于中断、

从 GPIO 模块中、180个事件/中断可作为 GPIO 中断 XBAR 的输入、如下图所示。

180个输入包含独立的 GPIO 中断(4个 GPIO 模块的144个复用)以及4个 GPIO 模块的9个组中断

| 中断数量 | |

| 单个 GPIO 引脚中断 | 144. |

| 针对实例0的 GPIO 组中断 | 9. |

| 针对实例1的 GPIO 组中断 | 9. |

| 实例2的 GPIO 组中断 | 9. |

| 实例3的 GPIO 组中断 | 9. |

| 中断总数 | 180 |

在当前 SDK 8.5中、我们有 使用 GPIO 组中断的 GPIO_INPUT_INTERRUPT 示例。

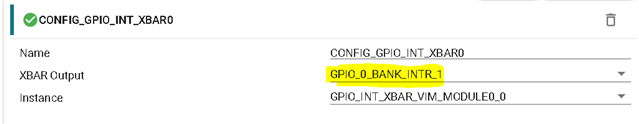

在该示例中、转到 SYSCFG -> GPIO INT XBAR 选项。

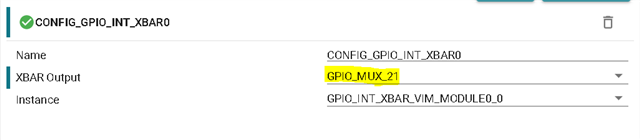

要使用单独的 GPIO 中断、请将 XBAR 输出选项更改为您所需的相应 GPIO_MUX 引脚。 在这里、忽略此上下文中的"_MUX"、这仅指单独的 GPIO 引脚。

在确认和检查单个和组 GPIO 中断的中断状态时、可以使用以下 API:

| GPIO 组 | 各个 GPIO |

| GPIO_getBankIntStatus | GPIO_IntgetStatus |

| GPIO_clearBankIntStatus | GPIO_IntclearStatus |