尊敬的 TI:

在使用 TM4C 期间、我们存在以下问题、需要您的帮助来提供建议。

有2块电路板:

- MCU 板(仅 MCU + BT5芯片)

- 主板(工业接口(4-20mA、0-10V、I/O、以太网)

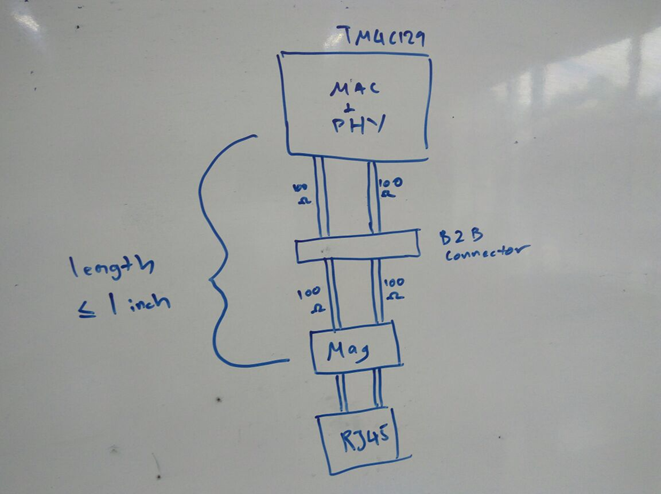

MCU 板通过高速 B2B 连接器连接到主板。 请注意、主板没有 MCU/MPU。

我们担心差分对从 Magnetics+RJ45 (Magjack)到 B2B 连接器再到 TM4C129x (PHY 引脚)的路由。

1.使用 TM4C 内部 PHY–主板上有 magjack

2.使用普通的 MCU 并将外部 PHY 放置在主板上

详细说明如下。

我们想知道以下配置是否会影响以太网性能并产生干扰?

还是使用下图所示的外部 PHY IC 更好:

我们的理解是 RMII/MII 信号不太容易受到噪声的影响、通过 B2B 连接器路由 RMII/MII 会导致问题更少。

请帮助提供进一步的建议。