您好!

首先,我要解释,我已经看到了一些类似这个问题的帖子。 我仍然对我的系统中发生的情况以及问题的根源有一些疑问。

我在 配置为 ADC (MCP3428-E/ST)的单主模式下使用 TM4C123BH6PZ、总线上的上拉电阻为4.99K 欧姆。 总线以100KHz 运行。

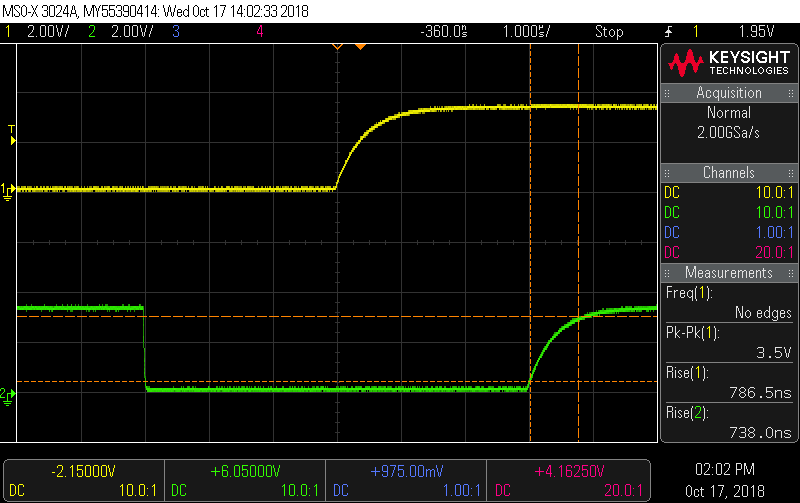

我的问题是他:我观察到一个很短的时钟脉冲、似乎混淆了 MCU 和 ADC 之间的时序、这导致 ADC 在等待停止位时将 SDA 保持在低电平。 请参阅下面的捕获。 遗憾的是、我只能使用逻辑分析仪捕获此错误。 测得的 runt 脉冲的脉冲宽度为.2599uS。

从阅读有关 tm4c 存在类似问题的其他用户的信息、我仍然不清楚问题的根源是什么。 tm4c 毛刺脉冲滤波器是否仅处理 SCL/SDA 上的输入、或者毛刺脉冲滤波器是否也可以滤除 SLC 输出上的这些短脉冲?

这是否是 tm4c 的已证实问题(如果有、是否有诊断和解决方案?)、或者我的固件或硬件更有可能出现这种问题? 我读过一位用户声称、降低上拉电阻值解决了问题、因为 runt 脉冲的上升时间不符合规格、所以 MCU 正在尝试重新建立正确的通信。 如果在我的系统中发生这种情况(因为我有4.99k 而非传统的4.7K 上拉电阻)、为什么所有 SCL 脉冲的上升时间不会减慢、而只是几个随机脉冲?

欢迎您提出任何想法/建议、谢谢!