主题中讨论的其他器件:INA240

在发现精度误差 的一部分后、ADC0 与 周期性模拟信号触发的采样步骤 POP 相关、进入特定阵列单元格的值为零。 实际值的数字转换接近2mV 模拟信号、但对0x0000进行了采样。

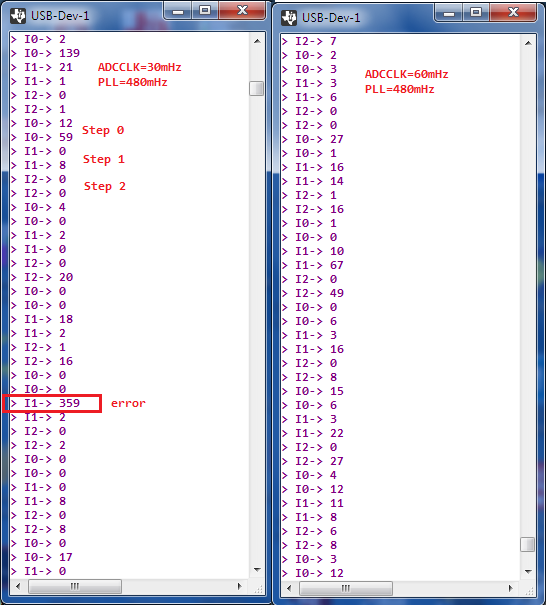

使用 本应为480MHz 的 PLL 将 ADCCLK 加速到据信为60MHz 的频率可提高 ADC 采样精度。 如果 ADCCLK 为30MHz 甚至60MHz、在许多样本中的默认值远远超过0x0000、精度如何提高到2MSPS? 模拟信号 具有非常干净的采集点。 当通过 GPTM 触发序列发生 器时、AD 转换器在模拟信号上产生的采集粒度似乎要比通过 PWM0 GEN0触发的采样粒度更高、而 PWM0 GEN0会产生80us 的模拟信号峰值。 此外、POP 进入阵列单元的值仅将稳态信号斜升至 2mV 的阈值(200mA)、但拒绝斜升至低于 先前 POP 的 VREFP-VREFN 值、即使初始斜率从0v 上升 至2mV。 如果便宜的6000计数1.2kHz DMM 可以轻松 测量该相同的电流(向上/向下)比例、则 TM4C 精密 ADC 可以轻松地实现 PIE、对吧? 该 DMM 绝不具有 TM4C 宣称 具有的精密 ADC、因此 序列发生器配置中必须存在完全错误的情况。

ADCSSFSTAT TPTR 索引与 FIFO 数据的实际 POP 对齐不会影响下面的0x0缺失的采集。 在 模拟信号接近 并达到稳定状态后或期间、AD 转换器绝不应产生0x0的完整字符串、对吧? AD 转换实际上是通过生成一个比下面显示的更多的0字符串开始的。

尽管据说 VCO 正在生成两个时钟 以及 60MHz PWMCLK、但 SYSCLK 和 ADCCLK 似乎在不同的时域中存在时序问题。 如果不通过对 ADC 模块进行超频来提高 MCU 温度 、如何实现60MHz ADCCLK?它在下图中?