您好!

我知道这一主题已经在几个主题(e2e.ti.com/.../569566)中讨论过

但是、我仍然缺少问题根源的解释、因此我的情况如下。

我将 TM4C129用作 I2C 主设备。 毛刺脉冲滤波器设置为8 (在120MHz 的系统时钟下运行)、I2C 的频率为100kHz

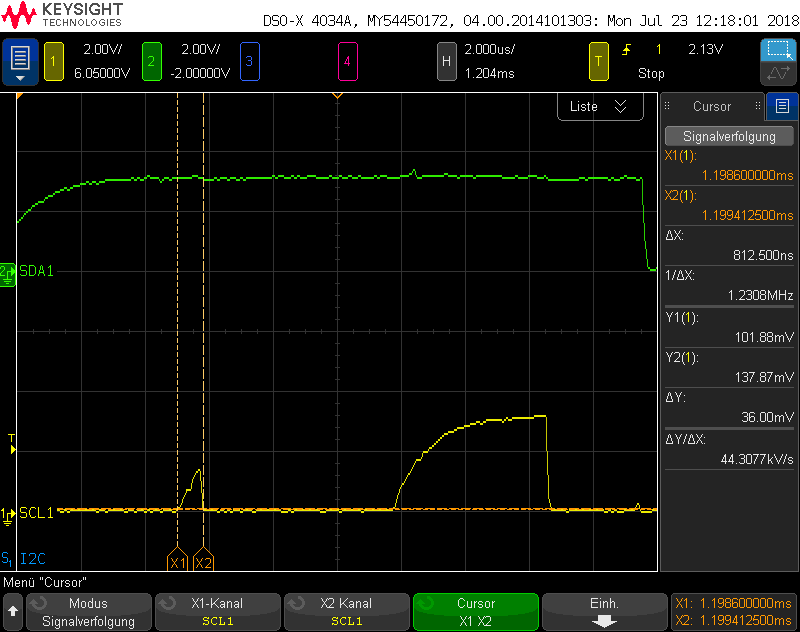

那么、我在这里看到的情况与其他具有短 SCL 脉冲的线程中描述的情况相同:

我知道信号质量相当差、时钟的上升时间超出限制。

但我不理解的是、主器件中止启动时钟边沿并将其拉低的原因。 此时、我100%确定主器件将 SCL 通道保持在低电平、因为从属器件在执行时钟扩展时使用不同的低电平。

我的电流假设是、SCL 的上升时间对于主器件来说太慢、因此它假定一个从器件将时钟保持在低电平。 然后主器件将 SCL 自身保持为低电平、以保持 SCL 切换的常规时序。 但是、我在数据表中找不到有关此行为的任何信息。

那么、您能否确认我的理论、或者如果错误、您能否解释 TM4C 主器件在中止时钟边沿后将时钟保持在低电平的情况?

非常感谢

Fabian