主题中讨论的其他器件:REF2033

您好!

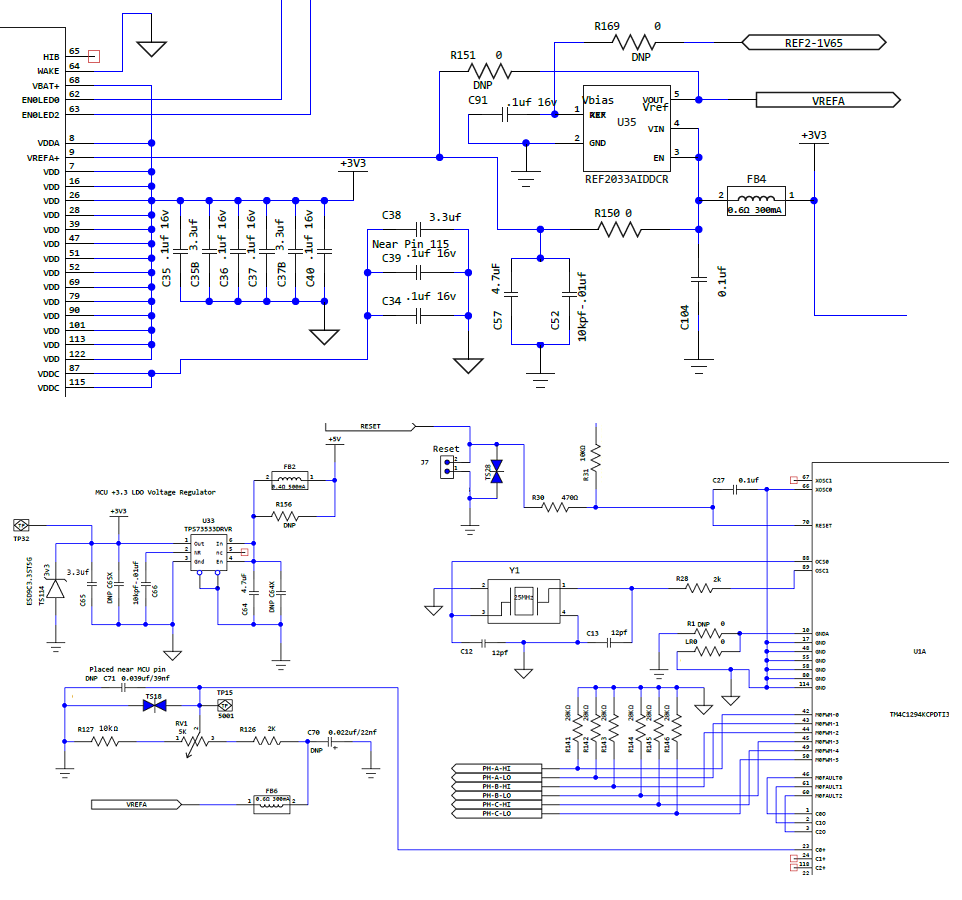

另一个 MCU 早已无法 通过 REF2033为外部模拟比较器 C0+(PC6)供电。 请注意 、通过 RV1的 C0+阈值设置为2.54v (<3V3)、但 VDDA 引脚8至 10 GNDA 为 (12欧姆)、MCU 电路外。 在检测到几个不必要的 C0+故障以某种方式导致 MCU 故障后、只需触摸 TP15上的 DMM 探针即可检查 C0+阈值。 请注意 、佩戴静电 腕带和 PCB 外周箔 迹线 连接 到接地、 导致静电可疑 。

除了几个 TVS 二极管之外、这两个二极管都不会停止任一 MCU 故障。 ADC0/1 都是在 VREFA+内部配置的。 从+3V3直接为 FB6供电不会导致 MCU 早期故障、但允许瞬变进入 C0+输入、 RE2033似乎提供 瞬态隔离。 REF2033由与 VDD 相同的+3V3 LDO 供电。 LR0 是0r 芯片 、甚至 是到 DGND 的硬焊球、 在事后剖析 故障分析中没有任何影响。

配置是什么 也会导致 VDD 对 DGND 短路(<1.3 Ω)、MCU 不电路? 配置 模拟比较器 CnO (或输出 OD)是否与 C0+外部电源有问题? 由 直接+3V3供电的其他配置 VR1 (C0+)连续工作 了数 月 、没有出现故障。 我们是否可以声称这些 MCU 故障?