大家好、

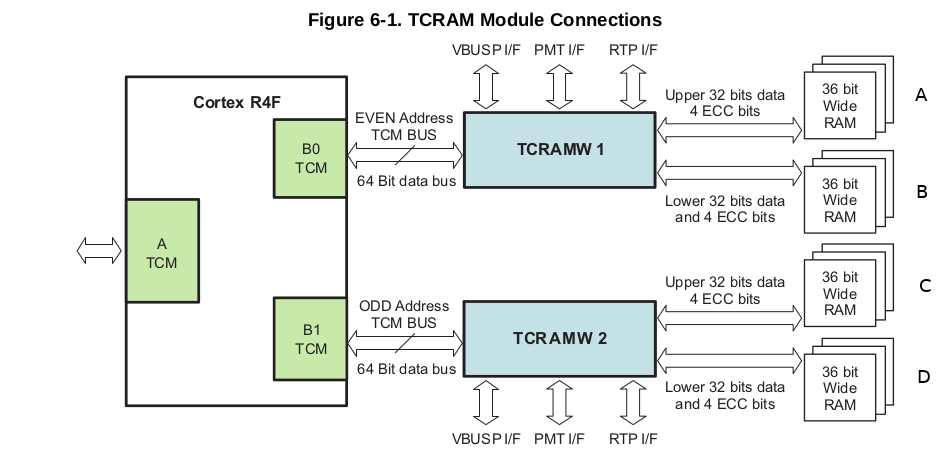

RM48x 技术参考手册(SPNU503B–2012年11月–2013年8月修订版本 p 297)中的下图提出了一些问题。

以下是我了解和理解的内容:

- 只消耗两个 Cortex R4F 中的一个、第二个 Cortex R4F 还具有其自己的 B0TCM 和 B1TCM。

- 从 ARM Cortex-R4F 技术参考手册中、我发现一个 R4F 允许有两个 BTCM 接口、这两个 BTCM 接口在这两个接口上交错

- 地址的位[3]

- 对 MSB 的影响

- RM48L952具有两个 RAM 组

RM48L952产品说明书(SPNS177D–2011年9月–2015年6月修订版 p 85)的以下句子使我感到困惑。

TCRAM 的特性:

"通过实现两个36位宽字节交错 RAM 组、为 RAM 寻址提供了增强的安全性

并向两个存储体生成独立的 RAM 访问控制信号"

但是、在图片上、我看到4个36位宽的 RAM (我标记为 A、B、C、D)。

我不理解这张图片和我引述的句子之间的关系。

以下是几个具体问题:

1) 1)有多少个 RAM 组?

2) 2) A、B、C 和 D 如何适应这些组?

3) 3)如果我声明 uint8_t array[16]={0x00、0x11、0x22、0x33、0x44。 0xFF};

这是如何存储在存储器组(或存储区)中/划分在存储器组中的? ABCD)?

提前感谢、

此致。

Karel