大家好、

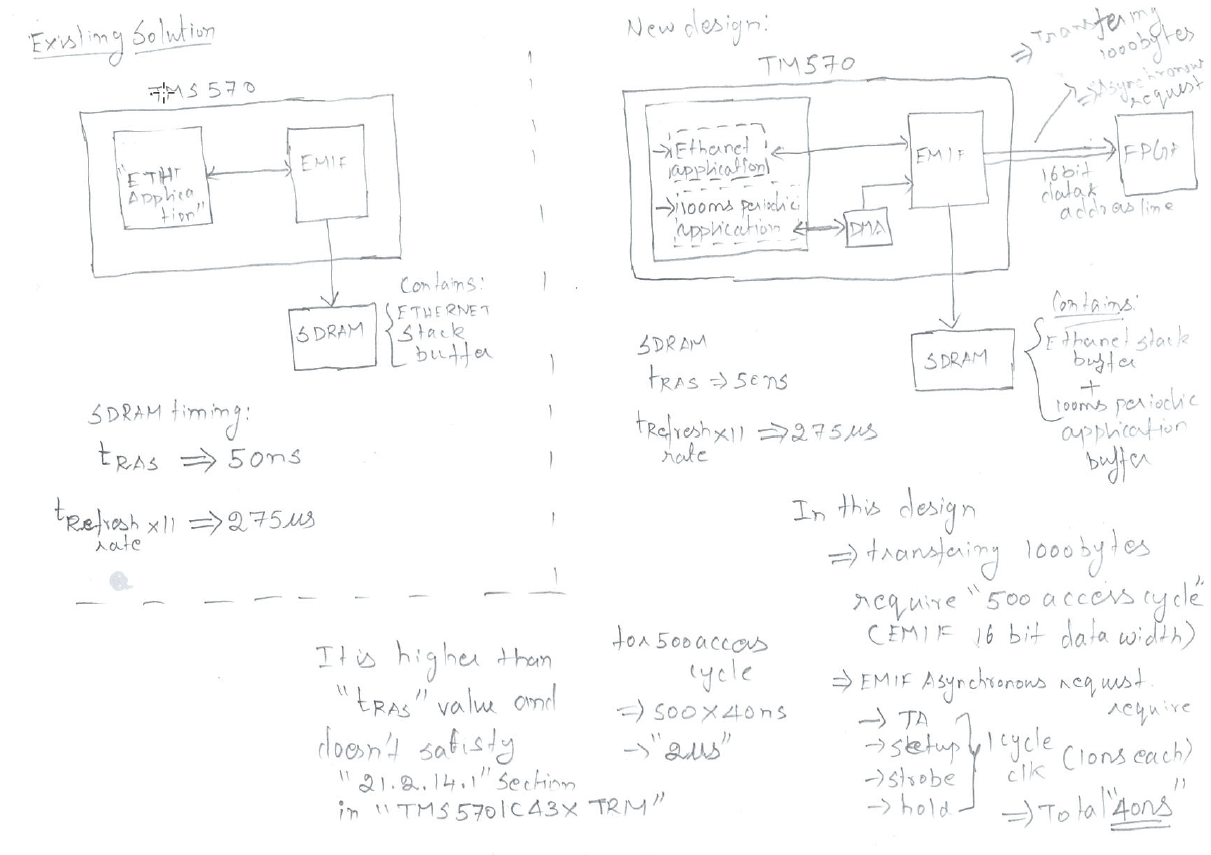

现有解决方案:

1) 以太网接收数据字节并存储在 SDRAM (EMIF 同步模式)中

新设计:

1) 以太网接收数据字节并存储在 SDRAM (EMIF 同步模式)中

2) 100ms 周期性应用将请求 DMA 通过 EMIF 接口(异步模式)将1000字节的数据从 SDRAM (EMIF 同步模式)传输到 FPGA。

问题:

如图所示、对于传输1000个字节、我们需要500个异步访问周期(EMIF 16位数据)。

每个异步周期为40ns (设置、保持、选通、TA -每个都为10ns)。 因此、对于500个异步访问周期、需要500 * 40ns = 2us。

符合第21.2.14.1节 TMS570LC43x TRM 的要求

异步请求< TRAAS。

2us < 50ns ->条件不满足。 这种理解是否正确? 请分享您对此的看法。

谢谢。