主题中讨论的其他器件:TL081、 LM741

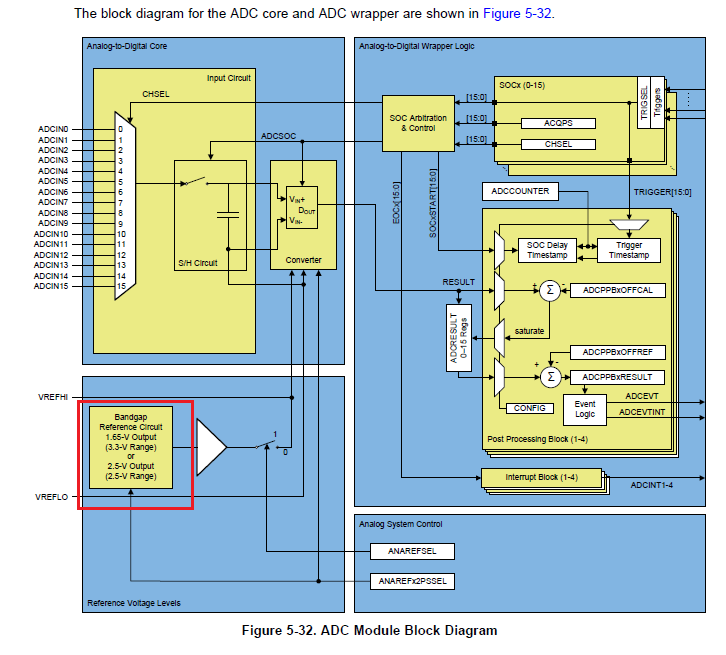

对于满量程 VREFN、ADC 是否具有1.65v 带隙内部基准 、对于设置为单端输入模式的通道、ADC 是否具有 VREP +3V3?

1.65V 带隙内部基准的优势是什么、如果 VREFP 中点附近的样片不存在、则会出现错误负载?

其他 TI 工程师使用下面的 ADC 模块来确定所有 SAR 型 ADC 的 MID VREFP 传感器功能、这对于 TM4C1294而言似乎有问题。

当选择1.65V 内部基准电压时、有效 ADC 转换输入范围将为 VREFLO 至3.3V。