主题中讨论的其他器件:UNIFLASH、 SysConfig、 CCStudio

各位专家、您好!

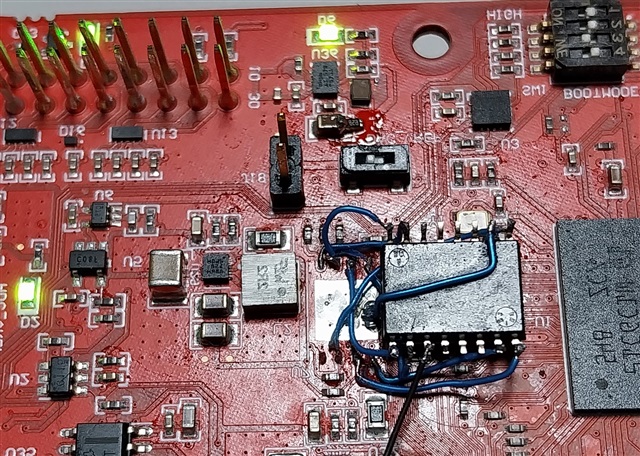

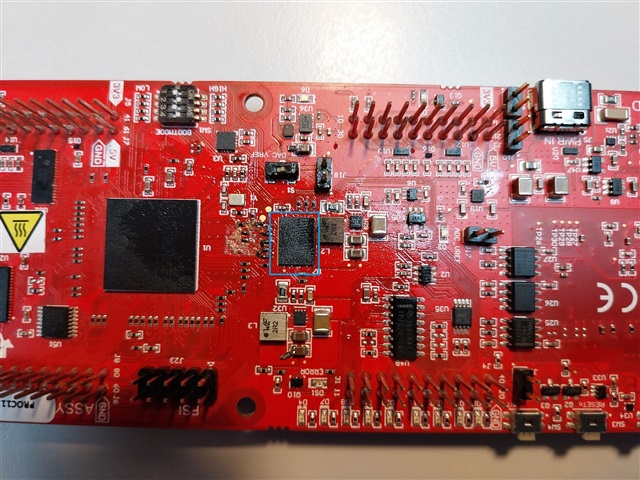

我们 正在尝试使用 MT25QL512ABB 这个闪存。 我们 将其放在 LP-AM263x 上并运行 QSPI_FLASH_diag_am263x 演示项目、然后获取 json 文件作为附件。

[Cortex_R5_0] [QSPI Flash Diagnostic Test] Starting ...

[QSPI Flash Diagnostic Test] Flash Manufacturer ID : 0x20

[QSPI Flash Diagnostic Test] Flash Device ID : 0xBA20

[QSPI Flash Diagnostic Test] Executing Flash Erase on first block...

[QSPI Flash Diagnostic Test] Done !!!

[QSPI Flash Diagnostic Test] Performing Write-Read Test...

[QSPI Flash Diagnostic Test] Write-Read Test Passed!

[QSPI Flash Diagnostic Test] SFDP Information :

================================================

SFDP

================================================

SFDP Major Revision : 0x1

SFDP Minor Revision : 0x6

Number of Parameter Headers in this Table : 2

Types of Additional Parameter Tables in this flash

---------------------------------------------------

4 BYTE ADDRESSING MODE INSTRUCTIONS TABLE

{

"flashSize": "67108864",

"flashPageSize": "256",

"flashManfId": "0x20",

"flashDeviceId": "0xBA20",

"flashBlockSize": "65536",

"flashSectorSize": "4096",

"cmdBlockErase3B": "0xD8",

"cmdBlockErase4B": "0xDC",

"cmdSectorErase3B": "0x20",

"cmdSectorErase4B": "0x21",

"protos": {

"p111": {

"isDtr": false,

"cmdRd": "0x03",

"cmdWr": "0x02",

"modeClksCmd": 0,

"modeClksRd": 0,

"dummyClksCmd": 0,

"dummyClksRd": 0,

"enableType": "0",

"enableSeq": "0x00",

"dummyCfg": null,

"protoCfg": null,

"strDtrCfg": null,

},

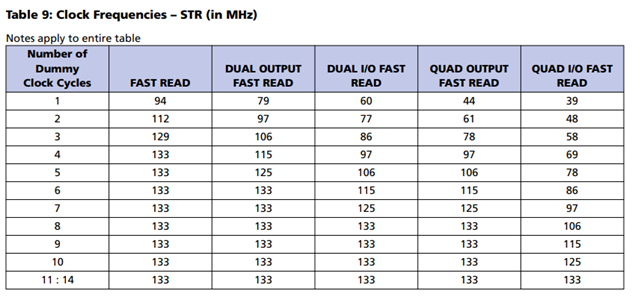

"p112": {

"isDtr": false,

"cmdRd": "0x3C",

"cmdWr": "0x02",

"modeClksCmd": 0,

"modeClksRd": 1,

"dummyClksCmd": 0,

"dummyClksRd": 7,

"enableType": "0",

"enableSeq": "0x00",

"dummyCfg": null,

"protoCfg": null,

"strDtrCfg": null,

},

"p114": {

"isDtr": false,

"cmdRd": "0x6C",

"cmdWr": "0x34",

"modeClksCmd": 0,

"modeClksRd": 1,

"dummyClksCmd": 0,

"dummyClksRd": 7,

"enableType": "0",

"enableSeq": "0x00",

"dummyCfg": null,

"protoCfg": null,

"strDtrCfg": null,

},

"p118": null,

"p444s": null,

"p444d": null,

"p888s": null,

"p888d": null,

"pCustom": null

},

"addrByteSupport": "1",

"fourByteAddrEnSeq": "0x36",

"resetType": "0x3D",

"cmdWren": "0x06",

"cmdRdsr": "0x05",

"srWip": 0,

"srWel": 0,

"cmdChipErase": "0xC7",

"flashDeviceBusyTimeout": 128000000,

"flashPageProgTimeout": 120

}

All tests have passed!!

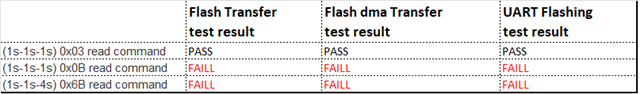

2.我们已检查以下设置

-检查1s-1s 模式(我们使用1s 模式),WEL 必须设置1。 -完成

-硬件可靠性 : 确保 Micron 闪存能够通过引导 QSPI_FLASH_DMS_TRANSFT (32KB)和 QSPI_FLASH_TRANSFT (256B)测试-通过

-增加超时值,因为 SPI 模式要慢得多-完成此操作

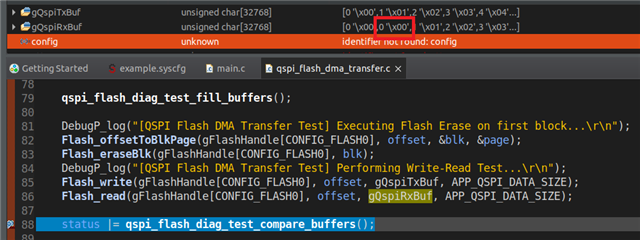

请找到我们配置的最终设置。

/* FLASH Attrs */

/* FLASH Attrs - populated from SysConfig options */

Flash_Attrs gFlashAttrs_MT25QL512ABB =

{

.flashName = "MT25QL512ABB",

.deviceId = 0xBA20,

.manufacturerId = 0x20,

.flashSize = 67108864,

.blockCount = 1024,

.blockSize = 65536,

.pageCount = 256,

.pageSize = 256,

.sectorCount = 16384,

.sectorSize = 4096,

};

/* FLASH DevConfig */

/* FLASH DevConfig - populated from SysConfig options */

Flash_DevConfig gFlashDevCfg_MT25QL512ABB =

{

.enable4BAddr = false,

.addrByteSupport = 0x00,

.fourByteAddrEnSeq = 0x00,

.cmdWren = 0x06,

.cmdRdsr = 0x05,

.srWip = (1 << 0),

.srWel = (1 << 1),

.resetType = 0x1D,

.eraseCfg = {

.blockSize = 65536,

.sectorSize = 4096,

.cmdBlockErase3B = 0xD8,

.cmdBlockErase4B = 0xD8,

.cmdSectorErase3B = 0x20,

.cmdSectorErase4B = 0x20,

.cmdChipErase = 0xC7,

},

.idCfg = {

.cmd = 0x9F, /* Constant */

.numBytes = 3,

.dummy4 = 0,

.dummy8 = 0,

},

.protocolCfg = {

.protocol = FLASH_CFG_PROTO_1S_1S_1S,

.isDtr = FALSE, /* DTR not supported in this version of flash driver with QSPI */

.cmdRd = 0x03,

.cmdWr = 0x02,

.modeClksCmd = 0,

.modeClksRd = 0,

.dummyClksCmd = 0,

.dummyClksRd = 0,

.enableType = 0xFF,

},

.flashWriteTimeout = 4000,

.flashBusyTimeout = 128000000,

};

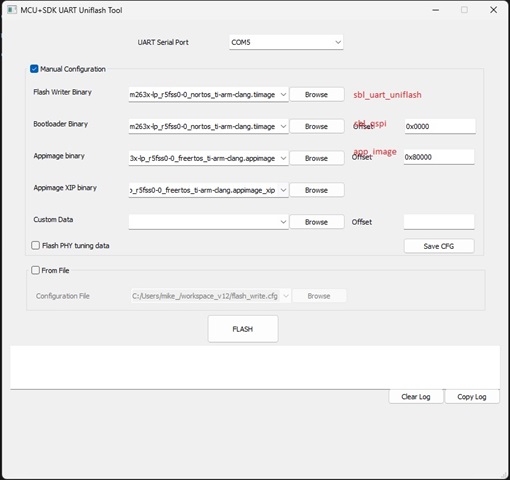

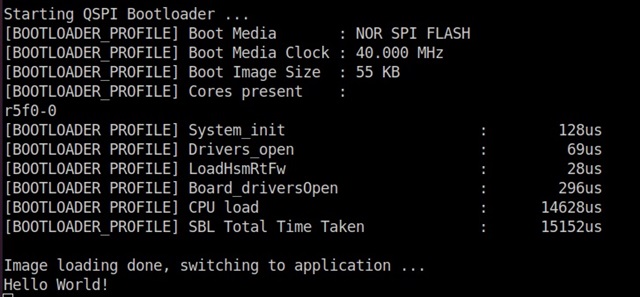

但是、我们目前遇到的问题是、我们可以使用闪存写入器将映像写入 Micron 闪存、但我们无法启动 SBL。

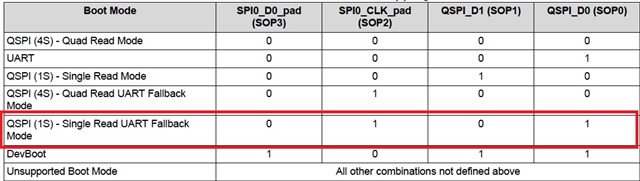

我们设置 QSPI (1S)-单读 UART 回退模式、但在重新启动电源后、SBL 无法启动、因此通过 UART 接口从外部主机启动。