主题中讨论的其他器件:ADS7038-Q1、 ADS7038

您好!

基于正在进行的主题:

我曾尝试将 DMA 序列请求从1.25us 放宽到5us。 为此、我确实希望 EDMA 将外部 SPI-ADC 的4通道请求突发写入 MCSPI 片上元件的 FIFO。 但如果这样做、SPI-TX 方向在几次传输后"消失"。 EDMA3配置为使用 ABSYNC 模式来执行此操作。 我在芯片勘误表(i2350)中读到、相对于 MCSPI 片上 IP、此 DMA 模式似乎存在问题。 然而,我不是真正理解的含义的描述。 我想利用这项工作。 然而、没有什么更好的发生。 因此、我认为我确实出错了。 如果希望在我的示例中在 MCSPI 内使用 EDMA + FIFO 模式的权变措施、有任何提示。

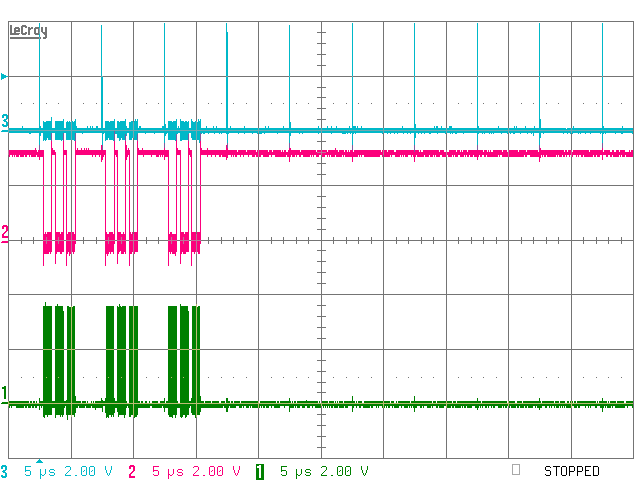

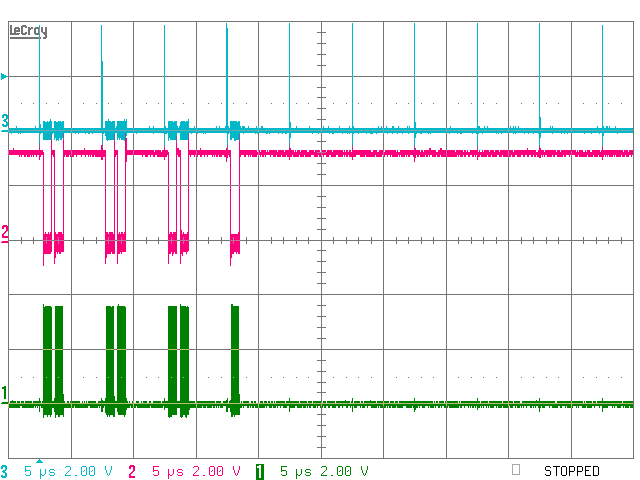

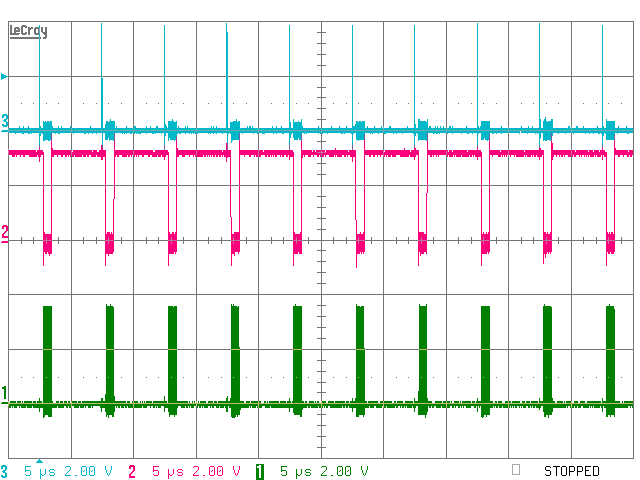

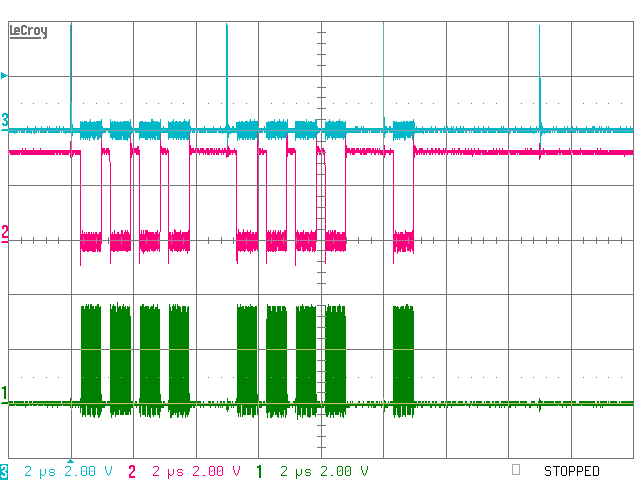

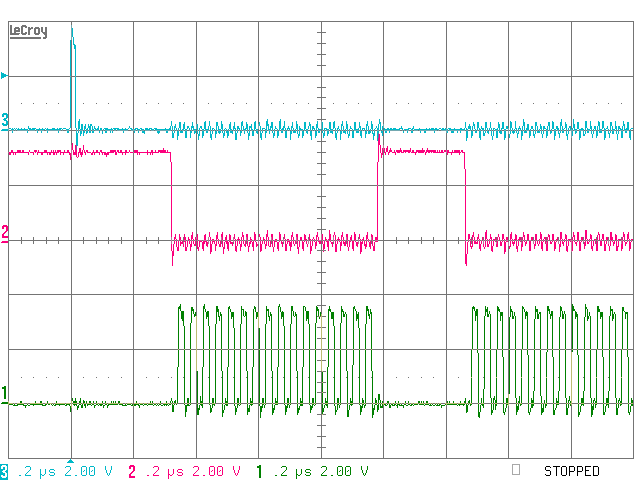

图例:

- Ch3 (蓝色) : EDMA 每5 us 触发一次

- Ch2 (品红色):MCSPI SPI-CSN 输出。 它相对于 SPI-Clk 以最大速度运行

-通道1 (绿色) : MCSPI SPI-Clk. SPI-Clk 频率为25MHz。

两个5us SPI 突发序列可以正常工作。 那么它就消失了。 不再有 SPI-Tx 活动。 根本原因未知。 EDMA 触发仍每5us 发生一次(蓝色迹线)。 EDMA3配置为在此通道上无限运行。

示波器屏幕截图与第一张屏幕截图相同。 不过已经放大了。 在此设置中、SPI-CSN (品红色布线)并不满足 ADS7038-Q1在大于1us 的片选周期时间方面的所有要求。 ADS7038 SPI-CSN 高电平时间> 230ns、满足低电平时间> 400ns 的要求。 违反了少量 ADC 采样周期。 但是、降低 SPI-Clk 频率可以(!) 从而形成一个能够满足所有时序要求的组合。

我确实配置了 EDMA 通道以便进行传输、从而将4个字(16位字)写入 MCSPI 的 FIFO。 这将每5微秒发生一次。 它确实会按预期启动。 但经过两个序列后、它消失了。 这是否与芯片勘误表(i2350)中所述内容有关?

Br

Markus