我正在尝试实现 I2C 读取函数来支持 KT0806L_v1.8 FM 调制器器件、 在 MSP432项目中需要一个重复的启动条件。

我运行的是 Bluetopia Stack v4.4.1.1。 但是、当尝试执行具有重复起始条件的读取时、写入工作正常、由于在向写入命令发送地址值之后外设希望发送停止条件、因此我遇到问题。 这将导致序列结束、并且读取返回无效数据。

我已经读取了许多线程、并且已经看到您必须如何在最后一个字节输出之前通过切换模式进行接收等来欺骗 TX ISR 内部的外设 示例驱动程序库(如下)就是这样尝试的、但这对默认示例工程不起作用:

C:\temp\msp432_driverlib_3_21_00_05\msp432_driverlib_3_21_00_05\examples\MSP432P4xx\i2c\i2c_master_rw_repeed_start-master_code。

我能够获得此论坛上的用户提供的以下代码以在独立的示例项目中工作:

但是、当我将它移植到我的 A3DPDemo_src 项目时、它不起作用。 停止条件由外设生成并终止重复启动条件、从而全部中断读取函数、并导致 KT Micro 设备上的状态机返回错误数据进行读取。

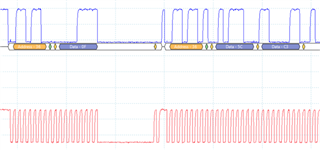

这是一本很好的读物、它使用了我从上面的链接获得的示例代码。 您可以看到停止条件发生、读取操作会恢复有效值。

在 My Project 中添加相同的代码时 、您可以看到停止条件出现、读取返回错误数据:

此外、该序列永不结束、使外设处于未知状态。

我注意到 I2C 外设非常依赖时序、因此我想补充一点、示例代码以3MHz MCLK 速度运行、波特率为100Kbps、而我的项目具有24MHz 时钟和100Kbps 波特率。 我基本上试图将代码中的延迟增加8倍、但这不起作用。

这是我将用于示例项目和我正在开发的项目的代码。

//Turn on FM Mod

GPIO_setOutputHighOnPin(GPIO_PORT_P4, GPIO_PIN6);

//GPIO_setOutputHighOnPin(HRDWCFG_FM_EN_PORT_NUM, HRDWCFG_FM_EN_PIN_NUM);

GPIO_setAsOutputPin(GPIO_PORT_P4, GPIO_PIN6);

/* Disabling the Watchdog */

MAP_WDT_A_holdTimer();

/* Select Port 1 for I2C - Set Pin 6, 7 to input Primary Module Function,

* (UCB0SIMO/UCB0SDA, UCB0SOMI/UCB0SCL).

*/

MAP_GPIO_setAsPeripheralModuleFunctionInputPin(GPIO_PORT_P1,

GPIO_PIN6 + GPIO_PIN7, GPIO_PRIMARY_MODULE_FUNCTION);

/* Initializing I2C Master to SMCLK at 400kbs with no autostop */

MAP_I2C_initMaster(EUSCI_B0_BASE, &i2cConfig);

/* Specify slave address */

MAP_I2C_setSlaveAddress(EUSCI_B0_BASE, SLAVE_ADDRESS);

/* Set Master in transmit mode */

//MAP_I2C_setMode(EUSCI_B0_BASE, EUSCI_B_I2C_TRANSMIT_MODE);

/* Enable I2C Module to start operations */

MAP_I2C_enableModule(EUSCI_B0_BASE);

__delay_cycles(10000);

/* Send out start + address + 1 data byte */

MAP_I2C_masterSendMultiByteStart(EUSCI_B0_BASE, TXData);

//wait for first byte to be moved to shift register

while(!(EUSCI_B0->IFG & EUSCI_B_IFG_TXIFG));

EUSCI_B0->IFG &= ~(EUSCI_B_IFG_TXIFG);

// Before the restart is sent, app has to wait for current TX byte + ack to complete

// This takes 9 cycles at 100kHz = 90uS

// The MCLK default = ~3MHz

// to complete the 1 byte TX app needs to wait ~270 MCLK cycles at a minimum

__delay_cycles(300);

//clear the TR bit to setup master as receiver

EUSCI_B0->CTLW0 &= ~(EUSCI_B_CTLW0_TR);

// Send the start + address

EUSCI_B0->CTLW0 |= EUSCI_B_CTLW0_TXSTT;

// wait for address to be sent

while(!(EUSCI_B0->CTLW0 & EUSCI_B_CTLW0_TXSTT));

// set stop immediately to ensure only one byte is read

EUSCI_B0->CTLW0 |= EUSCI_B_CTLW0_TXSTP;

// poll RX flag

while(!(EUSCI_B0->IFG & EUSCI_B_IFG_RXIFG0));

// Read from Receive buffer

RXData = EUSCI_B0->RXBUF;

// ensure I2C transaction has completed

while (MAP_I2C_masterIsStopSent(EUSCI_B0_BASE));

提前感谢您帮助我解决这个问题。