"Thread: SysConfig"中讨论的其他器件

大家好、

我将定制 AM2434_ALV 处理器与4GB DDR4连接、引脚配置与 AM2434 EVM 板相同。

我有以下关于 DDR4的问题

- 我想使用处理器配置 DDR。 为了完成此操作、我必须实施哪些设置?

- 我已尝试使用默认 AM2434_EVM DDR 脚本、它卡在随附的映像中。

请引导我。

--

谢谢。此致、

Divyesh Patel

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我将定制 AM2434_ALV 处理器与4GB DDR4连接、引脚配置与 AM2434 EVM 板相同。

我有以下关于 DDR4的问题

请引导我。

--

谢谢。此致、

Divyesh Patel

尊敬的 Divyesh:

GEL 文件中的 DDR 初始化适用于 AM243x EVM 上使用的 DDR (8MB)。 对于定制电路板上使用的 DDR、您可能需要根据尺寸、时序等进行调整。 该文件 为位于的 AM243x EVM 执行 DDR 初始化

C:\ti\ccs1200\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x_GP_EVM.gel

此致、

Ming

尊敬的 Divyesh:

DDR4配置工具和文档的情况并不理想。 以下是我们目前拥有的资源:

1.转到 SysConfig (TI.com) 并添加一个新的 DDR4实例

2.使用生成的 AM243x-DDRConfig.gel 替换 C:\ti\ccs1200\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x-DDR4-1600MTs.gel

3.重新运行 load_dmcdc.js 和 AM2434_EVM DDR 脚本。

您还可以调整以下各项:

1. DDR 存储器类型

2.系统配置

3. DRAM 计时 A/B

4. IO 控制 A/B

此致、

Ming

尊敬的 Ming:

对于 DDR 配置、我曾提到 ">software-dl.ti.com/.../DRIVERS_DDR_PAGE.html"。

已使用尝试全部3种方法

但我无法生成.gel 文件

如何生成.gel 文件? 请指导我执行了哪些错误步骤。

--

谢谢。此致、

Divyesh Patel

尊敬的 Divyesh:

它也应该适用于 CCS 11.1。 请尝试我在上一篇文章中建议的步骤:

----------------

DDR4配置工具和文档的情况并不理想。 以下是我们目前拥有的资源:

1.转到 https://dev.ti.com/sysconfig/?product=Processor_DDR_Config&device=AM243x_beta 并添加一个新的 DDR4实例:

2.使用生成的 AM243x-DDRConfig.gel 替换 C:\ti\ccs1200\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x-DDR4-1600MTs.gel

3.重新运行 load_dmcdc.js 和 AM2434_EVM DDR 脚本。

您还可以调整以下各项:

1. DDR 存储器类型

2.系统配置

3. DRAM 计时 A/B

4. IO 控制 A/B

----------------

此致、

Ming

尊敬的 Ming:

我已经创建了.gel 文件、并在给定的链接中替换

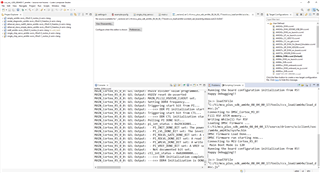

使用生成的 AM243x-DDRConfig.gel 替换 C:\ccs1200\ccs\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x-DDR4-1600MTs.gel[/报价]然后、从"Scripts"->"AM24 DDR Initialization "->"AM24 DDR Initialization DDR"运行脚本、两者都启用/禁用、但仍然根据附加的映像卡住

根据附加的图像、这是第二次发生故障

我甚至尝试过采用默认 SDK 配置的 TMDS243GPEVM、但仍然遇到问题

请引导我。

--

谢谢。此致、

Divyesh Patel

尊敬的 Divyesh:

DDR4配置非常复杂、并且高度依赖于所使用的 DDR4。

对于 AM243x GP EVM、您可以使用最新的 MCU+ SDK 08.05.00.24和 CCS12试用它。

最好的酒保

Ming

尊敬的 Ming:

感谢您的答复。

时是否已根据您的 DDR4芯片调整了 DDR4设置

是的、我已经根据我的 DDR4芯片完成了所有配置。

我将尝试使用 CCS1200。

另一个困惑是、我曾尝试使用 EVM、但其中也出现错误

我甚至尝试过采用默认 SDK 配置的 TMDS243GPEVM、但仍然遇到问题

[/报价]

为什么会这样?

它应与 EVM 配合使用根据 EVM 配置了 bcz SDK、然后说明为什么会出错

请帮助我有关这个,它可能给我一些提示我的问题。

—

谢谢。此致、

Divyesh Patel

尊敬的 Divyeh:

我认为这可能与目标配置文件和 load_dmsc.js 有关。 我针对 AM64x 尝试了具有 MCU+ SDK 08.04.00.17的 CS12.0.0、使用 AM64x GP EVM 而不是 AM243 GP EVM 作为默认目标配置。 它可以与以下脚本正常配合使用:

loadJS 文件"C:/ti/mcu_plus_sdk_am64x_08_04_00_17/tools/ccs_load/am64x/load_dmsc.js "

然后是 DDR 初始化。

顺便说一下、AM243x GP EVM 一个 AM64x G EVM 的物理性质相同。

此致、

Ming

尊敬的 Ming:

我已经使用 AM2434 EVM 成功完成了 DDR 初始化测试、写入和读取测试。

但在我的定制板中、初始化和写入测试已完成、但无法完成读取测试。

请检查我的日志并帮助我离开。

DMSC_Cortex_M3_0: GEL Output: This GEL is currently only supported for use from the Cortex-M3 inside the DMSC. DMSC_Cortex_M3_0: GEL Output: Do not run this GEL from any other CPU on the SoC. DMSC_Cortex_M3_0: GEL Output: This script sets the first address translation region to [0x8000_0000, 0x0000_0000]. DMSC_Cortex_M3_0: GEL Output: It also sets the second address translation region to [0x6000_0000, 0x4000_0000]. DMSC_Cortex_M3_0: GEL Output: This is consistent with the SoC DV assumptions. DMSC_Cortex_M3_0: GEL Output: Configuring ATCM for the R5Fs DMSC_Cortex_M3_0: GEL Output: ATCM Configured. DMSC_Cortex_M3_0: GEL Output: R5F Halt bits set. DMSC_Cortex_M3_0: GEL Output: Configuring bootvectors DMSC_Cortex_M3_0: GEL Output: Bootvectors configured. DMSC_Cortex_M3_0: GEL Output: Programming all PLLs. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 0 (Main PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 0 (Main PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 1 (Peripheral 0 PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 1 (Peripheral 0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 2 (Peripheral 1 PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 2 (Peripheral 1 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 8 (ARM0 PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 8 (ARM0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 12 (DDR PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 12 (DDR PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 14 (Main Domain Pulsar) PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 14 (Main Domain Pulsar PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming MCU PLL 0 (MCU PLL) DMSC_Cortex_M3_0: GEL Output: MCU PLL 0 (MCU PLL) Set. DMSC_Cortex_M3_0: GEL Output: All PLLs programmed. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains in progress... DMSC_Cortex_M3_0: GEL Output: Powering up MAIN domain peripherals... DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DMSC DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_PBIST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_4B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_8B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_USB DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ADC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DEBUGSS DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_GPMC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_CFG DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_DATA DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SA2UL DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SERDES_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PCIE_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_0 DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_CPSW3G DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW done. DMSC_Cortex_M3_0: GEL Output: Powering up all MAIN domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN2MCU DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCU2MAIN DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_M4F DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains done! DMSC_Cortex_M3_0: GEL Output: DMSC_Cortex_M3_0: GEL Output: M4F WFI Vector set into IRAM. MAIN_Cortex_R5_0_0: GEL Output: Running from R5 MAIN_Cortex_R5_0_0: GEL Output: DDR not initialized with R5 connect. Go to menu Scripts --> AM64 DDR Initialization -> AM64_DDR_Initialization_ECC_Disabled to initialize DDR. ==== MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is in progress ... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> ECC Disabled <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address slice 2 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> Set PHY registers for all FSPs simultaneously (multicast)... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Frequency not supported by GEL MAIN_Cortex_R5_0_0: GEL Output: Setting DDR4 frequency... MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from PI... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from CTL... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR CTL initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Polling PI DONE bit... MAIN_Cortex_R5_0_0: GEL Output: pi_int_status = 0x29C02001... MAIN_Cortex_R5_0_0: GEL Output: - PI_INIT_DONE_BIT set: The power-on initialization training in PI has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_LVL_DONE_BIT set: The leveling operation has completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_GATE_DONE_BIT set: A read leveling gate training operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_DONE_BIT set: A read leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_WRLVL_DONE_BIT set: A write leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_VREF_DONE_BIT set: A VREF setting operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - Not documented bit set. MAIN_Cortex_R5_0_0: GEL Output: ctl_int_status = 0x02000004... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR Initialization completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is DONE! <<<--- MAIN_Cortex_R5_0_0: GEL Output: Starting Writes Test... MAIN_Cortex_R5_0_0: GEL Output: ...DDR Writes test Done! MAIN_Cortex_R5_0_0: GEL Output: Starting Reads Test: MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x03020100 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x04030201 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: DDR Reads test Done! MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 1: *wr32_ptr=i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x00000000 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x01010101 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 2: *wr32_ptr=~i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x030100FF Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x0100FFFE Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: !!!!! DDR Basic read/write test Failed !!!!

哪种配置可能会导致此问题?

请帮我解决。

--

谢谢。此致、

Divyesh Patel

您好、James:

感谢您的建议。

请尝试使用:cl=14和 cwl = 9

我尝试过、但仍然有相同的错误。 是否有任何其他参数放置错误?

--

谢谢。此致、

Divyesh Patel

GEL 有问题。 第137行显示"Frequency not supported by GEL"

在 CCS 中、您能找到"Help->About Code Composer Studio->Installation Details->Sitara Device Support 吗? 版本号是什么? 我认为最新版本是1.6.3、看看您是否可以更新那个软件包并重试。

如果这样不起任何作用、请压缩目录 C:\ti\ccs1200\ccs\ccs_base\emulation\gel\am24x、然后在此处发帖、我将来看一下。

此致、

詹姆斯

您好、James:

在 CCS 中,您能提供帮助吗->关于 Code Composer Studio->安装详细信息-> Sitara 设备支持吗? 版本号是什么?

我的 Sitara 器件支持版本为 v1.6.1。 更新时通知没有更新、因此我认为它是最新版本。

我已附加 am24x 和 am64x 文件。

目前我使用的是 am64x 配置、因为之前在尝试使用 am24x 时、无法初始化 DDR、并卡在"轮询 PI DONE 位"中

然后、从"Scripts"->"AM24 DDR Initialization "->"AM24 DDR Initialization DDR"运行脚本、两者都启用/禁用、但仍然根据附加的映像卡住

[/报价]

请帮我解决。

--

谢谢。此致、

Divyesh Patel

您好,Divyesh,更新似乎也不起作用! 让我们完全替换所有凝胶:

-rename C:\ti\ccs1200\ccs_base\emulation\gel\am64x 改为 am64x_old

-将附件解压缩 到同一目录,这样你就可以得到一组新的 gels for am64x

-您可能需要为您的开发板重新生成目标配置

-像以前一样执行 DDR init 和读/写测试(确保脚本控制台中没有运行 javascripts)

-如果控制台输出仍不工作,请发送该输出

/cfs-file/__key/communityserver-discussions-components-files/908/0358.AM64x.zip

此致、

詹姆斯

JJD、您好!

我尝试了上述配置、但仍然收到相同的错误。

PFA 控制台输出。

DMSC_Cortex_M3_0: GEL Output: This GEL is currently only supported for use from the Cortex-M3 inside the DMSC. DMSC_Cortex_M3_0: GEL Output: Do not run this GEL from any other CPU on the SoC. DMSC_Cortex_M3_0: GEL Output: This script sets the first address translation region to [0x8000_0000, 0x0000_0000]. DMSC_Cortex_M3_0: GEL Output: It also sets the second address translation region to [0x6000_0000, 0x4000_0000]. DMSC_Cortex_M3_0: GEL Output: This is consistent with the SoC DV assumptions. DMSC_Cortex_M3_0: GEL Output: Configuring ATCM for the R5Fs DMSC_Cortex_M3_0: GEL Output: ATCM Configured. DMSC_Cortex_M3_0: GEL Output: R5F Halt bits set. DMSC_Cortex_M3_0: GEL Output: Configuring bootvectors DMSC_Cortex_M3_0: GEL Output: Bootvectors configured. DMSC_Cortex_M3_0: GEL Output: Debugging enabled DMSC_Cortex_M3_0: GEL Output: Programming all PLLs. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 0 (Main PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x000003FF DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x000003FF DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 10 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000000 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00000000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 9 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 24 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 14 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #5 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 4 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #5 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #6 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #6 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #7 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #7 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #8 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #8 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #9 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 2 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #9 programmed. DMSC_Cortex_M3_0: GEL Output: Selected Main Domain PLL Controller. DMSC_Cortex_M3_0: GEL Output: Cleared bit 0 in the PLL controller control register. DMSC_Cortex_M3_0: GEL Output: Cleared bit 5 in the PLL Controller control register. DMSC_Cortex_M3_0: GEL Output: PLL controller is now in bypass mode. DMSC_Cortex_M3_0: GEL Output: Set reset isolation to prevent a warm reset from killing the PLL controller. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: addr: 0x80410124 = 0x00008000 DMSC_Cortex_M3_0: GEL Output: Clear GOSET. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: Set ALN1. DMSC_Cortex_M3_0: GEL Output: addr: 0x80410104 = 0x00000012 DMSC_Cortex_M3_0: GEL Output: Set OCSEL to 0x12, point C on the observation clock input tree inside the PLL Controller. DMSC_Cortex_M3_0: GEL Output: addr: 0x80410148 = 0x00000002 DMSC_Cortex_M3_0: GEL Output: Set the clock control register to enable the OBSCLK output (bit 1). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 1. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Enable PLL Controller (write to bit 0 in control register). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 0. DMSC_Cortex_M3_0: GEL Output: PLLCTRL reset is cleared. PLLCTRL is free. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 0 (Main PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 1 (Peripheral 0 PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x0000007F DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x0000007F DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 7 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000001 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00001000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 9 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 11 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 4 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 9 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 79 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #5 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #5 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #6 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 15 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #6 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 1 (Peripheral 0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 2 (Peripheral 1 PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x000003FF DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x000003FF DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 10 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000002 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00002000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: i: 1, HSDIV value is -1, don't program this one DMSC_Cortex_M3_0: GEL Output: HSDIV clock output disabled. DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 8 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 17 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #5 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #5 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #6 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #6 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #7 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 17 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #7 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #8 DMSC_Cortex_M3_0: GEL Output: i: 8, HSDIV value is -1, don't program this one DMSC_Cortex_M3_0: GEL Output: HSDIV clock output disabled. DMSC_Cortex_M3_0: GEL Output: HSDIV #8 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #9 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 4 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #9 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 2 (Peripheral 1 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 8 (ARM0 PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x00000001 DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x00000001 DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 1 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000008 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00008000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 1 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 8 (ARM0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 12 (DDR PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x00000001 DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x00000001 DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 1 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x0000000C DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x0000C000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 12 (DDR PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 14 (Main Domain Pulsar) PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x00000003 DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x00000003 DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 2 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x0000000E DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x0000E000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 2 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 2 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 14 (Main Domain Pulsar PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming MCU PLL 0 (MCU PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x0000001F DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x0000001F DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 5 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x04040000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000000 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00000000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 24 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 24 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 11 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 11 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Selected MCU Domain PLL Conntroller. DMSC_Cortex_M3_0: GEL Output: Cleared bit 0 in the PLL controller control register. DMSC_Cortex_M3_0: GEL Output: Cleared bit 5 in the PLL Controller control register. DMSC_Cortex_M3_0: GEL Output: PLL controller is now in bypass mode. DMSC_Cortex_M3_0: GEL Output: Set reset isolation to prevent a warm reset from killing the PLL controller. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: addr: 0x84020124 = 0x00008000 DMSC_Cortex_M3_0: GEL Output: Clear GOSET. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: Set ALN1. DMSC_Cortex_M3_0: GEL Output: addr: 0x84020104 = 0x00000012 DMSC_Cortex_M3_0: GEL Output: Set OCSEL to 0x12, point C on the observation clock input tree inside the PLL Controller. DMSC_Cortex_M3_0: GEL Output: addr: 0x84020148 = 0x00000002 DMSC_Cortex_M3_0: GEL Output: Set the clock control register to enable the OBSCLK output (bit 1). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 1. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Enable PLL Controller (write to bit 0 in control register). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 0. DMSC_Cortex_M3_0: GEL Output: PLLCTRL reset is cleared. PLLCTRL is free. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: MCU PLL 0 (MCU PLL) Set. DMSC_Cortex_M3_0: GEL Output: All PLLs programmed. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains in progress... DMSC_Cortex_M3_0: GEL Output: Powering up MAIN domain peripherals... DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DMSC DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_PBIST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_4B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_8B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_USB DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ADC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DEBUGSS DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_GPMC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_CFG DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_DATA DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SA2UL DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SERDES_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PCIE_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_CLUSTER_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_CLUSTER_0 DMSC_Cortex_M3_0: GEL Output: ERROR: module state NOT changed! DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_CLUSTER_0_PBIST DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_CLUSTER_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_0 DMSC_Cortex_M3_0: GEL Output: ERROR: module state NOT changed! DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_1 DMSC_Cortex_M3_0: GEL Output: ERROR: module state NOT changed! DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_0 DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_CPSW3G DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW done. DMSC_Cortex_M3_0: GEL Output: Powering up all MAIN domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN2MCU DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCU2MAIN DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_M4F DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains done! DMSC_Cortex_M3_0: GEL Output: DMSC_Cortex_M3_0: GEL Output: *****DDR is configured using R5 or A53 GELs DMSC_Cortex_M3_0: GEL Output: M4F WFI Vector set into IRAM. MAIN_Cortex_R5_0_0: GEL Output: Running from R5 MAIN_Cortex_R5_0_0: GEL Output: DDR not initialized with R5 connect. Go to menu Scripts --> AM64 DDR Initialization -> AM64_DDR_Initialization_ECC_Disabled to initialize DDR. ==== MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is in progress ... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> ECC Enabled <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> After priming ECC memory, enable ECC_CK bit with hotmenu AM64 DDR Memory config --> Enable_TI_InlineECC_CK_During_Reads()<<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address slice 2 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> Set PHY registers for all FSPs simultaneously (multicast)... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Debugging enabled MAIN_Cortex_R5_0_0: GEL Output: Setting MAIN_PLL12_HSDIV0_CLKOUT_400MHz MAIN_Cortex_R5_0_0: GEL Output: hsdiv_value: 3 MAIN_Cortex_R5_0_0: GEL Output: HSDIV reset asserted MAIN_Cortex_R5_0_0: GEL Output: HSDIV divider value programmed. MAIN_Cortex_R5_0_0: GEL Output: HSDIV reset de-asserted MAIN_Cortex_R5_0_0: GEL Output: MAIN_PLL12_HSDIV0_CLKOUT set. MAIN_Cortex_R5_0_0: GEL Output: Setting DDR4 frequency... MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from PI... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from CTL... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR CTL initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Polling PI DONE bit... MAIN_Cortex_R5_0_0: GEL Output: pi_int_status = 0x29C02001... MAIN_Cortex_R5_0_0: GEL Output: - PI_INIT_DONE_BIT set: The power-on initialization training in PI has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_LVL_DONE_BIT set: The leveling operation has completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_GATE_DONE_BIT set: A read leveling gate training operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_DONE_BIT set: A read leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_WRLVL_DONE_BIT set: A write leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_VREF_DONE_BIT set: A VREF setting operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - Not documented bit set. MAIN_Cortex_R5_0_0: GEL Output: ctl_int_status = 0x02000004... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR Initialization completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is DONE! <<<--- MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 1: *wr32_ptr=i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x00000000 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x01010101 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 2: *wr32_ptr=~i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x030100FF Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x0100FFFE Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: !!!!! DDR Basic read/write test Failed !!!!

以及是否需要从以下路径更改 board_ddrReginit.h 文件

C:\ti\mcu_plus_sdk_am243x_08_04_00_17\source\drivers\ddr\v0\soc\am64x_am243x

因为它 在 SysConfig 的自述文件中提及。

请帮我解决。

--

谢谢。此致、

Divyesh Patel

最终、需要更改 board_ddrReginit.h、但在使用 gel 初始化电路板时不应使用它。 这就是我问是否使用和 javascripts 的原因。 确保您没有在脚本控制台中运行任何 javascript 文件。 此外、确保在为电路板供电时没有从引导介质。 要确保这一点,请将引导模式设置为"No Boot Mode"(无引导模式),或确保已擦除或删除引导介质(如 SD 卡中所示)。 您是否正在运行任何 javascript 或无意中从引导介质引导?

最新配置失败后、是否可以使用以下 GEL 脚本发送寄存器转储: Scripts->AM64 DDRSS Debug->Memory Debug->AM64 DDRSS CTL PI PHY Memdump

此致、

詹姆斯

您好、James:

我正在运行初始化的 pfa load_dmsc.js。

为确保这一点,请将引导模式设置为"No Boot Mode"(无引导模式),或确保已擦除或删除引导介质(如 SD 卡)。 [/报价]它设置为无引导模式。

等待您的反馈。

--

谢谢。此致、

Divyesh Patel

您好、James:

PFA 更新了控制台输出。