主题中讨论的其他器件:UNIFLASH、 HALCOGEN

我正在实施引导加载程序、以通过 CAN 更新 RM46。 我已根据项目确定 TI 提供的示例 CAN 引导加载程序、已经相当成功。 现在我处于成功将接收到的映像写入闪存的阶段、我正在尝试引导至映像。 但是、当我执行此操作时、会受到预取系统中断(地址0x1002C)的影响。

一些背景信息:

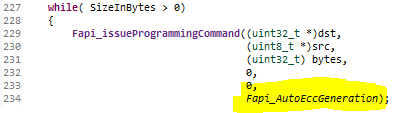

- 引导加载程序启用了 ECC (RAM)、但我目前为主应用程序禁用了 ECC (RAM 和闪存)。

- 主应用程序是 与 CCS 编程时工作的现有应用程序

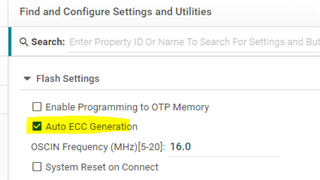

- 我没有在 CCS 中启用自动 ECC 生成功能

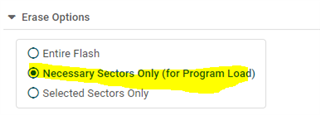

- I 仅擦除必要扇区(用于程序加载)

- 当我通过 Uniflash 加载引导加载程序和主应用程序时、我无法引导主应用程序(强制启动到应用程序)

- 我已经调整了主应用程序的链接器文件、以指向我认为是正确位置的内容。

- 我让引导加载程序的 sys_intvecs.asm 重定向至闪存中主应用程序的矢量位置。

下面您将找到两个链接器文件的副本、并附有 HALCoGen 项目文件。

主应用链接器 cmd 文件:

/*----------------------------------------------------------------------------*/

/* sys_link.cmd */

/* */

/*

* Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/* */

/*----------------------------------------------------------------------------*/

/* USER CODE BEGIN (0) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Linker Settings */

--retain="*(.intvecs)"

/* USER CODE BEGIN (1) */

/* IGNORE the generated Memory code, overridden below */

#if 0

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Memory Map */

MEMORY

{

VECTORS (X) : origin=0x00000000 length=0x00000020

FLASH0 (RX) : origin=0x00000020 length=0x0013FFE0

STACKS (RW) : origin=0x08000000 length=0x00005800

RAM (RW) : origin=0x08005800 length=0x0002a800

/* USER CODE BEGIN (2) */

#endif

/* Override Memory Segments with CRC here */

#if 1

MEMORY

{

VECTORS (X) : origin=0x00010020

length=0x00000020

vfill = 0xffffffff

CRCMEM (RX) : origin=end(VECTORS)

length=0x000001E0

vfill = 0xffffffff

FLASH0 (RX) : origin=end(CRCMEM)

length=(0x0013FFFF - end(CRCMEM))

vfill = 0xffffffff

STACKS (RW) : origin=0x08000000

length=0x00004c00

RAM (RW) : origin=0x08004c00

length=0x0002b400

#endif

#if 1

ECC_VEC (R) : origin=(0xf0400000 + (start(VECTORS) >> 3))

length=(size(VECTORS) >> 3)

ECC={algorithm=algoL2R4F021, input_range=VECTORS}

ECC_CRC (R) : origin=(0xf0400000 + (start(CRCMEM) >> 3))

length=(size(CRCMEM) >> 3)

ECC={algorithm=algoL2R4F021, input_range=CRCMEM }

ECC_FLA0 (R) : origin=(0xf0400000 + (start(FLASH0) >> 3))

length=(size(FLASH0) >> 3)

ECC={algorithm=algoL2R4F021, input_range=FLASH0 }

#endif

/* USER CODE END */

}

/* USER CODE BEGIN (3) */

/* IGNORE the generated Sections code, overridden below */

ECC

{

algoL2R4F021 : address_mask = 0xfffffff8 /* Address Bits 31:3 */

hamming_mask = R4 /* Use R4/R5 build in Mask */

parity_mask = 0x0c /* Set which ECC bits are Even and Odd parity */

mirroring = F021 /* RM57Lx and TMS570LCx are build in F021 */

}

#if 0

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Section Configuration */

SECTIONS

{

.intvecs : {} > VECTORS

.text : {} > FLASH0

.const : {} > FLASH0

.cinit : {} > FLASH0

.pinit : {} > FLASH0

.bss : {} > RAM

.data : {} > RAM

.sysmem : {} > RAM

/* USER CODE BEGIN (4) */

#endif

/* Override Sections with CRCs here */

#if 1

SECTIONS

{

.intvecs : {} > VECTORS, crc_table( _crc_table, algorithm=CRC32_C )

.text align(32) : {} > FLASH0, crc_table( _crc_table, algorithm=CRC32_C )

.const align(32) : {} > FLASH0, crc_table( _crc_table, algorithm=CRC32_C )

.cinit align(32) : {} > FLASH0, crc_table( _crc_table, algorithm=CRC32_C )

.pinit align(32) : {} > FLASH0

.bss : {} > RAM

.data : {} > RAM

.sysmem : {} > RAM

.TI.crctab : {} > CRCMEM

#endif

/* USER CODE END */

}

/* USER CODE BEGIN (5) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Misc */

/* USER CODE BEGIN (6) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

Bootloader 链接器 Cmd 文件:

/* Copyright (C) 2013-2019 Texas Instruments Incorporated - http://www.ti.com/ * * * Redistribution and use in source and binary forms, with or without * modification, are permitted provided that the following conditions * are met: * * Redistributions of source code must retain the above copyright * notice, this list of conditions and the following disclaimer. * * Redistributions in binary form must reproduce the above copyright * notice, this list of conditions and the following disclaimer in the * documentation and/or other materials provided with the * distribution. * * Neither the name of Texas Instruments Incorporated nor the names of * its contributors may be used to endorse or promote products derived * from this software without specific prior written permission. * * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR * A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT * OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, * SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT * LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, * DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY * THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT * (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. */ /* */ /*----------------------------------------------------------------------------*/ /* USER CODE BEGIN (0) */ /* USER CODE END */ /*----------------------------------------------------------------------------*/ /* Linker Settings */ --retain="*(.intvecs)" /* USER CODE BEGIN (1) */ /* USER CODE END */ /*----------------------------------------------------------------------------*/ /* Memory Map */ MEMORY { /* Bank 0 (384kB) */ VECTORS (X) : origin=0x00000000 length=0x00000020 vfill = 0xFFFFFFFF FLASH0 (RX) : origin=end(VECTORS) length=(0x00140000 - size(VECTORS)) vfill = 0xFFFFFFFF SRAM (RW) : origin=0x08002000 length=0x0002D000 STACKS (RW) : origin=0x08000000 length=0x00002000 /* USER CODE BEGIN (2) */ #if 1 /* Bank 0 ECC */ ECC_VEC (R) : origin=(0xf0400000 + (start(VECTORS) >> 3)) length=(size(VECTORS) >> 3) ECC={algorithm=algoL2R4F021, input_range=VECTORS} ECC_FLA0 (R) : origin=(0xf0400000 + (start(FLASH0) >> 3)) length=(size(FLASH0) >> 3) ECC={algorithm=algoL2R4F021, input_range=FLASH0 } #endif /* USER CODE END */ } /* USER CODE BEGIN (3) */ ECC { algoL2R4F021 : address_mask = 0xfffffff8 /* Address Bits 31:3 */ hamming_mask = R4 /* Use R4/R5 build in Mask */ parity_mask = 0x0c /* Set which ECC bits are Even and Odd parity */ mirroring = F021 /* RM57Lx and TMS570LCx are build in F021 */ } /* USER CODE END */ /*----------------------------------------------------------------------------*/ /* Section Configuration */ SECTIONS { .intvecs : {} > VECTORS flashAPI: { ./Fapi_UserDefinedFunctions.obj (.text) ./bl_flash.obj (.text) --library= "/home/fw/fwbl/flashAPI/F021_API_CortexR4_LE.lib" (.text) } palign=8 load = FLASH0, run = SRAM, LOAD_START(apiLoadStart), RUN_START(apiRunStart), SIZE(apiLoadSize) .text : {} > FLASH0 /*Initialized executable code and constants*/ .const : {} palign=8 load=FLASH0, run = SRAM, LOAD_START(constLoadStart), RUN_START(constRunStart), SIZE(constLoadSize) .cinit : {} > FLASH0 /*Initialized global and static variables*/ .pinit : {} > FLASH0 .data : {} > SRAM .bss : {} > SRAM /*Uninitialized Global and static variables */ .sysmem : {} > SRAM /* USER CODE BEGIN (4) */ /* USER CODE END */ } /* USER CODE BEGIN (5) */ /* USER CODE END */

e2e.ti.com/.../Bootloader-HCG.zip

引导加载程序 sys_intvecs.asm

;-------------------------------------------------------------------------------

; sys_intvecs.asm

;

; Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

;

;

; Redistribution and use in source and binary forms, with or without

; modification, are permitted provided that the following conditions

; are met:

;

; Redistributions of source code must retain the above copyright

; notice, this list of conditions and the following disclaimer.

;

; Redistributions in binary form must reproduce the above copyright

; notice, this list of conditions and the following disclaimer in the

; documentation and/or other materials provided with the

; distribution.

;

; Neither the name of Texas Instruments Incorporated nor the names of

; its contributors may be used to endorse or promote products derived

; from this software without specific prior written permission.

;

; THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

; "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

; LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

; A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

; OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

; SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

; LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

; DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

; THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

; (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

; OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

;

;

;

.sect ".intvecs"

.arm

;-------------------------------------------------------------------------------

; import reference for interrupt routines

.ref _c_int00

;-------------------------------------------------------------------------------

; interrupt vectors

; Please change the #0x???? for your specified image location defined in bl_config.h - 0x08

b _c_int00 ;0x00

b #0x10018 ;0x04 UNDEF; 0x10000-0x08

b #0x10018 ;0x08 SVC ; 0x10000-0x08

b #0x10018 ;0x0C PABT ; 0x10000-0x08

b #0x10018 ;0x10 DABT ; 0x10000-0x08

reservedEntry

b reservedEntry ;0x14, reserved

b #0x10018 ;0x18, irqDispatcher

ldr pc,[pc, #-0x1b0] ;0x1C, FIQ

;-------------------------------------------------------------------------------