主题中讨论的其他器件:SysConfig

BU 先生/女士、

客户在后台发现、在他们的板连续工作9天之后、他们基于计时器的周期性任务不再运行。

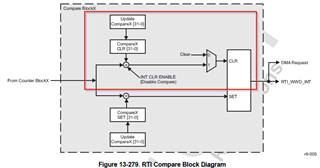

据我了解、芯片硬件内部有2个处理中断的阶段:RTI 中断生成逻辑+ VIM 中断优先级排序和处理。 满足 RTI INT 条件后、VIM IRQ STS 应置位并等待有效。

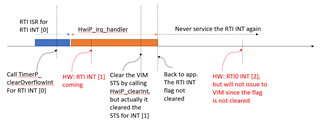

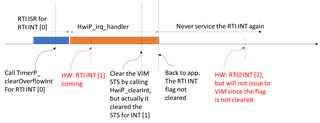

我编写了一个程序来了解硬件行为。 并且、从硬件运行来看、如果之前的 RTI INT 标志未被清除、相应的 VIM IRQ STS 将不会被置位。 为了更好地展现这一点、请参阅下图:

测试代码如下所示: e2e.ti.com/.../timer_5F00_int_5F00_not_5F00_handled.zip

我有以下想法:

1)。 出现此问题的根本原因是、当先前的 RTI INT 标志未清除时、后一个 RTI INT 将不会向 VIM 发出以设置 VIM INT STS、对吗?

2)。 将类型的属性从 Pulse 更改为 level 以解决此问题;

3)。 在 RTI 中启用定期标志清除功能来解决此问题。

请查看此问题并提供您的建议、谢谢。

Br、

将会