主题中讨论的其他器件:LP5890、 TLC6983

您好!

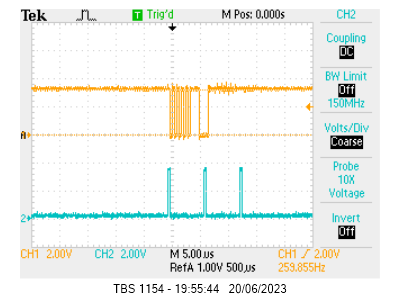

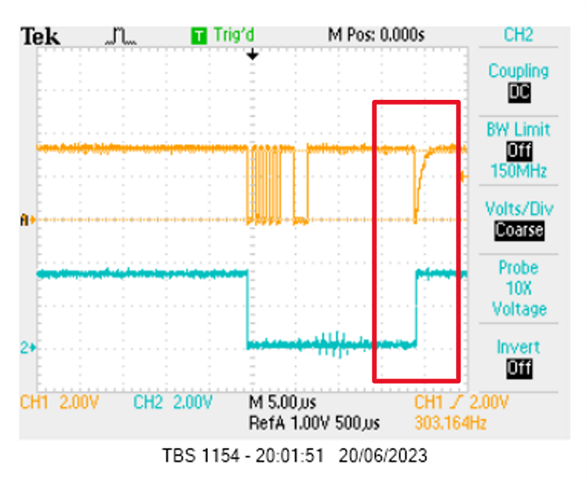

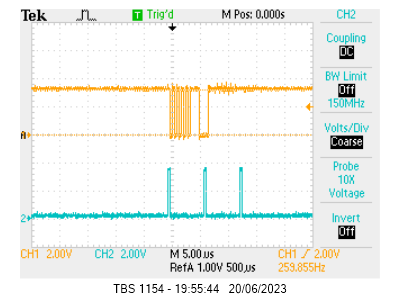

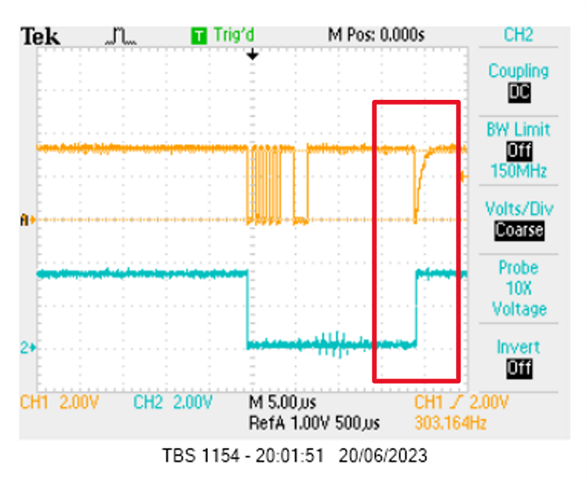

当 SSI1用作主机、 模式为 SSI_FRF_MOTO_MOTO_1或 SSI_FRF_MOTO_MODE_3时、 帧末尾串行输出引脚上的干扰会变为0V、正如 FSS 返回高电平一样。 使用 SSI_FRF_TI (TI 连续模式)时、我看不到任何干扰。 我使用10K 电阻器作为 串行 输出引脚的上拉电阻。 引脚配置是 TI PinMux 工具中用于 SSI1的引脚配置、无需进一步修改。

这是不是因为我做错了事?

谢谢。

马修

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

当 SSI1用作主机、 模式为 SSI_FRF_MOTO_MOTO_1或 SSI_FRF_MOTO_MODE_3时、 帧末尾串行输出引脚上的干扰会变为0V、正如 FSS 返回高电平一样。 使用 SSI_FRF_TI (TI 连续模式)时、我看不到任何干扰。 我使用10K 电阻器作为 串行 输出引脚的上拉电阻。 引脚配置是 TI PinMux 工具中用于 SSI1的引脚配置、无需进一步修改。

这是不是因为我做错了事?

谢谢。

马修

您好!

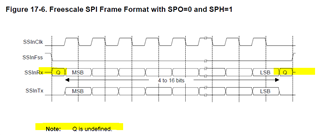

是使用 SSI 模块生成 FSS、还是通过 GPIO 生成 FSS? 在我看来、CS 信号的延长似乎比与 DATA 引脚进行比较时长得多。 您是否还可以将时钟添加到示波器中、从而使所有内容都清晰可见? 如果干扰超出有效芯片选择范围、则不应导致从器件将干扰误解为有效数据。 您能否确认从器件正确接收数据? 通常、不需要在 MOSI 引脚上添加一个上拉电阻器、但我认为这没有什么坏处。 我想是在 FSS 取消置位后、数据基本上是未定义的、可能是三态的。 根据迹线上的电容和10k 上拉电阻器、上拉至3.3V 可能需要一些 RC 延迟。

尊敬的 Charles:

感谢您的快速响应。

1. FSS 由 SSI 模块自动生成,帧恰好包含许多逻辑1! 可以通过我发送的另一个跟踪来验证这一点。

2.我同意通常情况下这不会造成问题,因为在流氓脉冲期间或之后没有时钟。 不过、我碰巧使用它和 PWM 生成的连续时钟来驱动 LP5890/TLC6983 LED 驱动器、因此此脉冲会使设备正常工作。 因为 TI 同步模式不存在此类问题、所以它可以很好地与连续时钟协同工作、我可以继续使用此模式。 我只是出于完整性考虑尝试了这些模式、如果它们在此应用中不起作用、这不是问题。

3.当我读取到引脚空闲时为三态、所以不希望它悬空时、我添加了上拉电阻器。

4.感谢您指出 Q =未定义的区域。 我没有注意到这一点。 这很好地解释了我看到了什么。

我真的只是想确保这不是我做错的事情、这似乎是 SSI 模块的预期行为。

此致、

马修