Other Parts Discussed in Thread: SYSCONFIG, TMDSCNCD263, AM2634

主题中讨论的其他器件:TMDSCNCD263、SysConfig、

尊敬的团队:

我使用的是 TMDSCNCD263评估板和来自 SDA 的 GPIO 中断示例、工作正常。

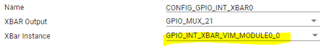

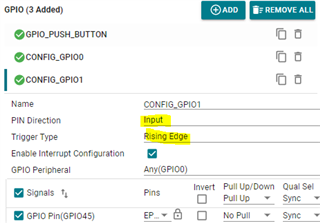

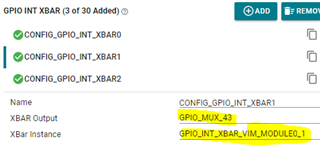

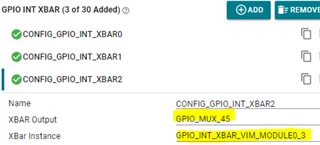

现在必须在 GPIO14、GPIO29、GPIO55和 GPIO78上配置更多中断、SysConfig 工具可用于配置这些引脚上的中断

Pinmux 最初根据 SDK 中的给定示例进行配置,遵循相同的过程, 如 GPIO_Init ()

现在的问题是"如何为各自的引脚配置 ISR?" 因为我按照显示的同样的过程在 GPIO_INPUT_INTERRUPT_MAIN (NULL)函数中配置 ISR。

我将对所有引脚使用相同的回调函数(这应该不是问题)

在示例中添加了代码、以在引脚中配置 ISR

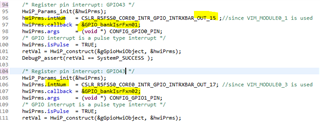

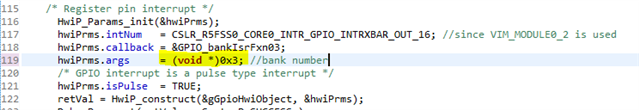

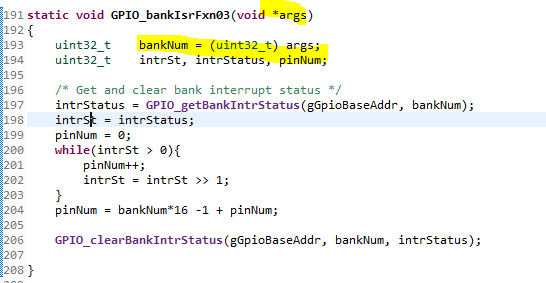

HwiP_Params_init (&hwiPrms1);

pinNum = CONFIG_GPIO0_PIN;

hwiPrms1.intNum = intrNum;

hwiPrms1.callback =&GPIO_bankIsrFxn;

hwiPrms1.args =(void *) pinNum;

hwiPrms1.isPulse = true;

RetVal = HwiP_structure (&gGpioHwiObject1、&hwiPrms1);

请指导如何正向状态来 为引脚配置 ISR 、因为读取数据表和配置 ISR 非常复杂