Other Parts Discussed in Thread: AM2632

您好!

我们正在使用 AM2632、我对启动流的可能性有疑问。

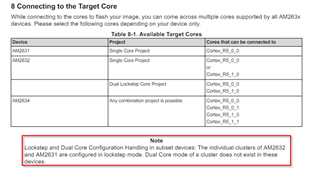

我们在锁步模式下使用 AM2632、因此我们有两个可用内核(R5SS0和 R5SS1)

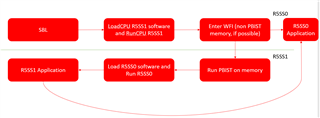

是否可以从 SBL 将固件加载到 R5SS1、然后在 R5SS1上启动固件。

在下一步中、R5SS1应将固件从闪存加载到 R5SS0、并在 R5SS0上启动。

是否可以将固件映像的此序列加载(SBL 加载到 R5SS1,从 R5SS0加载)?

我这个问题的背景是在将固件加载到 R5SS0之前在 R5SS1上执行 pBIST (测试 R5SS0存储器区域)。

此致

乔·肖