团队、您好!

我在 共享存储器段分配方面存在问题。

映射文件显示了存储器部分的预期地址。

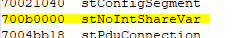

但当我加载符号时、 存储器段的地址与映射文件相比发生了变化。

*当我加载程序时,共享存储器段地址在硬件和类似的映射文件中是正确的。

链接器脚本:

EXCTABLE (RX):org = 0x70002000、len = 0x00000100

复位(RX):org = 0x70002100、len = 0x00000F00

闪存(rwx):org = 0x70003000、len = 0x00035000

RAM (rwx):org = 0x70038000、len = 0x00018000

FLASH_app (rwx):org = 0x70050000、len = 0x00050000

RAM_APP (rwx):org = 0x700A1000、len = 0x0000F000

RAM_shared (rwx):org = 0x700B0000、len = 0x00000400

.prog_sig:

{

/*------------------ PROG_SIG 部分--------------------------------------------------------------- */

__ SHRD_RAM_START =.;

*(.prog_sig)

__ SHRD_RAM_END =.;

}> RAM_SHARED

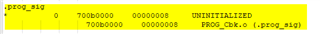

映射文件:

源码:

#define PROG_REPROG_FLAG_START_SEC_VAR_NO_INIT_8

#包含

#pragma clang 部分 bss=".prog_sig"

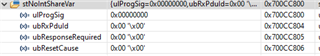

tNoIntShareVar stNoIntShareVar;

#define PROG_REPROG_FLAG_STOP_SEC_VAR_NO_INIT_8

#包含

硬件:

问)以下哪一项对于 TI Clang 编译器段的创建是正确的?

1) #pragma clang 部分 bss=".prog_sig"

tNoIntShareVar stNoIntShareVar;

2)

tNoIntShareVar stNoIntShareVar __attribute__((section (".prog_SIG"));

由于上述问题、项目在过去几天被阻止。

请您为我提供一些信息。

此致、

哈里