主题中讨论的其他器件: DP83869、 DP83822I

团队、您好!

EtherCAT 解决方案的一些主要特性。

我们是如何在 EtherCAT 解决方案中实施 EtherCAT 从站的、该解决方案是通过 TI 代码库获得的?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Chockalingam:

EtherCAT 子器件在具有 PRU-ICSS IP 的 TI SoC 上实现、使客户可以向其系统添加 EtherCAT 子器件协议支持。 它使用两个 MII 端口(每个 PRU-ICSS 一个输入和一个输出端口)根据 ETG.1000.4数据链路层协议规范实现 EtherCAT 子器件控制器(ESC)层2功能。 这就实现了集成到 TI SoC 中的类似 EtherCAT ASIC 的功能。

您可以在以下位置阅读更多相关信息: AM243x 工业通信 SDK:EtherCAT 子器件 FWHAL

如果您需要任何其他信息、请告诉我。

尊敬的 Santosh:

计划使用 DP83869HMRGZT (PHY)将每个端口的 MII 降低至 SMII (1Tx 和1RX)。 EtherCAT、profineti/o 和 EtherNet/IP 协议通信无论如何都会受到影响。

尊敬的 Santosh:

我们仅支持带有协议的 MII 和 RGMII、

谢谢你的答复,也许我没有问清楚的问题。

请参阅以下连接方框图并确认您的回复

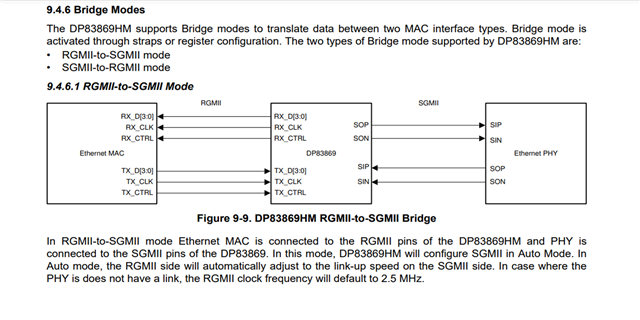

在方框图中、以太网 MAC 是 AM2434的一部分(具有 RGMII 接口) 、连接到 DP83869HMRGZT (PHY IC)、 后者将 RGMII 转换为 SGMII、继而 连接到 PHY (RJ45)

EtherCAT、Profinet 和 EtherNet/IP 协议通信无论如何都会受到影响?

在方框图中、以太网 MAC 是 AM2434的一部分(具有 RGMII 接口) 、连接到 DP83869HMRGZT (PHY IC)、 后者将 RGMII 转换为 SGMII、继而 连接到 PHY (RJ45)

EtherCAT、Profinet 和 EtherNet/IP 协议通信无论如何都会受到影响?

[/报价]PROFINET 和 EIP 在 RGMII 模式下工作。 但 EtherCAT 仅在 MII 模式下工作。 在桥接实施中、RGMII 连接到 MAC Profinet 和 EIP 将起作用、但 Ether cat 需要将 MII 连接到 MAC。

希望这可以回答您的问题、如果您有任何其他问题、请告诉我。

关于 AM2434发布 E3、我们将使用 DP83869HMRGZT (PHY IC)

据我们了解、对于 EtherCAT、

在上图中,我们可以看出 控制器 MAC 配置为 MII 模式,以及 PHY DP83869HMRGZT ( PHY IC 输入)配置为 MII 模式。 而在 DP83869HMRGZT 的另一侧(PHY IC 输出) 可以是 SGMII、在此 IC 中是否可以、如果可以、是否适用于 EtherCAT。

对于 EtherNet/IP 和 Profinet I/O、我们可以选择 RGMII (控制器 MAC)到 RGMII (PHYIC 输入)和 RGMII (PHYIC 输出)

下面是 TI am2434代码库中的代码片段、该代码片段在 DP83869HMRGZT (PHY IC)中设置 MII 模式。 但也可以在代码中配置 PHY 另一侧(输出侧)的 PHY 设置。

--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

void CUST_PHY_DP83869_setMIIMode (void * pAppCtxt_p、void * pStackCtxt_p)

{

phyRegVal = CUST_PHY_DP83869_readExtendedRegister (pAppCtxt_p、pStackCtxt_p、CUST_PHY_DP83869_OP_MODE_DED);

phyRegVal || CUST_PHY_DP83869_DATA_OPMODE_DECDE_MII;

CUST_PHY_DP83869_writeExtendedRegister (pAppCtxt_p、pStackCtxt_p、CUST_PHY_DP83869_OP_MODE_DECODED、phyRegVal);

}

--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

2.如果我们选择使用 dp83822i (Phy IC)、该器件支持 MII/RMII/RGMII 至 SMII。 对于 EtherCAT 和 EtherNet/IP、它的工作原理是选择 MII 到 MII。

它如何处理 Profinet i/o PROFINET/IRT IR -实时数据?

在上图中,我们可以确定 控制器 MAC 配置为 MII 模式,PHY DP83869HMRGZT (PHY IC 输入)配置为 MII 模式。 而在 DP83869HMRGZT (PHY IC 输出) 的另一侧可能是 SGMII、此 IC 中是否可行、如果是、是否适用于 EtherCAT。

尊敬的 Santosh、感谢您对此进行澄清、如上所述、如果您具有适用于 EtherCAT MAC 的 MII、那么它应该可以正常工作。 但是、在继续进行设计之前、请与 PHY 团队确认一次。 我没有从 MAC 端看到 RISC。

下面是 TI am2434代码库中的代码片段、该代码片段在 DP83869HMRGZT (PHY IC)中设置 MII 模式。 但也可以在代码中配置 PHY 另一侧(输出侧)的 PHY 设置。

--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

[/报价]

void CUST_PHY_DP83869_setMIIMode (void * pAppCtxt_p、void * pStackCtxt_p)

{

phyRegVal = CUST_PHY_DP83869_readExtendedRegister (pAppCtxt_p、pStackCtxt_p、CUST_PHY_DP83869_OP_MODE_DED);

phyRegVal || CUST_PHY_DP83869_DATA_OPMODE_DECDE_MII;

CUST_PHY_DP83869_writeExtendedRegister (pAppCtxt_p、pStackCtxt_p、CUST_PHY_DP83869_OP_MODE_DECODED、phyRegVal);

}我们不对 dp83869 phy 的桥接模式提供 SDK 支持、您需要与 phy 团队合作处理这些详细信息。

2.如果我们选择使用 dp83822i (Phy IC)、该器件支持 MII/RMII/RGMII 至 SMII。 对于 EtherCAT 和 EtherNet/IP、它的工作原理是选择 MII 到 MII。

它如何处理 Profinet i/o PROFINET/IRT IR -实时数据?

[/报价]PROFINET 还可与 MII 和 RGMII 配合使用、因此这不应成为难题。

如果您有任何其他疑问、请告诉我。