Other Parts Discussed in Thread: MSP432E401Y

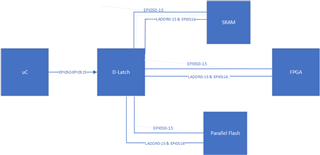

我目前正在设计一个采用 MSP432E401Y 的微控制器板、该板使用 EPI 主机总线多路复用模式与3个器件(SRAM、并行闪存和 FPGA)进行连接

为了分离地址和数据线,我应该为 EPI 添加一个 D 锁存器(见 https://www.ti.com/tool/TIDM-TM4CFLASHSRAM)。

或者内部 ALE 引脚将捕获地址并进行相应的发送?

如果直接将 EPI 管脚作为 A0-EPI0和 D0-EPI0与设备相连,是否可以正常工作?

如果我必须在硬件设计中添加任何内容、请告诉我