大家好!

我们有一些关于在 TI Sitara AM2432 Arm-Cortex M4内核上使用 SDL for ECC 的问题:

- 在 ECC SDL 示例中、 SDL_ECC_aggr1 (值3)作为 ECC init ( SDL_ECC_init ) API。 您能否提供有关此接口的更多信息?

- 为什么 aggr1作为 memtype 传递?

- 这些 memtypes 如何与物理内存链接?

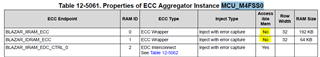

- 我们的目标是在 M4内核上执行 RAM 测试。 如果我们选择 memtype 作为 MCU_M4FSS0 (SDL_MCU_M4FSS0_BLAZAR_ECCAGGR)、并且我们想对 ECC 包装程序执行测试、我们如何对其进行测试? 在 TRM 文档中、该存储器显示为无法访问。

- 在 TRM 文档(请参考:表12-5051)中、我们可以看到6个 ECC 端点连接到 ECC aggr1。 但在示例中、ECC 初始化 API ( SDL_ECC_init) ,它仅选择给定 ECC 终点以下的2。

IAM64_MAIN_EDC_CBASS_MAIN_0_AM64_MAIN_INFRA_CBASS_IK3VTM_N16FFC_MAIN_0_VBUSP_P2P_BRIDGE_IK3VTM_N16FFC_MAIN_0_VBUSP_BRIDGEC 和 IAM64_MAIN_CBUS_MAIN_0_AM64_MAX_MAIN_IQ4_SYSCLKUS_MAIN_CRCS_4_SYSL_4_CBISS_MI_SL_SL_SL_4_CSCL_CBISS_MAIN_MI_C_BUSCC_4)。

其他 ECC 端点情况如何? - SDL_ECC_init API 与 SDL_ECC_initMemory API 之间的确切区别是什么?

我们的理解是、必须调用 SDL_ECC_initMemory 多次以初始化多个 ECC 端点、其中、我们可以调用 SDL_ECC_init 一次以初始化多个 ECC 端点。 请说明 - 数字隔离器与接收器之间的 SDL_ECC_注射错误 API 和 SDL_ECC_自检 API? 请澄清以下要点。

- 我们是否可以使用 SDL_ECC_自检 运行时的 API。 我们的理解是、由于它是一个阻塞调用、因此只能在启动期间使用它。

- 我们的理解是、 SDL_ECC_自检 API‘"重试次数"和‘"中断处理机制"、在发生 SDL_ECC_注射错误 API 进行配置。

- 在 ECC 的示例中、清楚地展示了如何使用安全 MCU 在 ECC 互连上注入错误、 SDL_ECC_注射错误 结构。 ECC 包装程序的方式是否相同?

- 您能向我们提供有关不同 Checker‘Group ID’(组 ID)和‘Checker Type’(检查类型)的更多信息吗?

- 奇偶校验、冗余和错误检测以及正确。

- 我们是否需要在每个 Checker 组 ID 上注入错误并进行验证?

谢谢。

路易斯