您好、我在使用 TMS570LC4357芯片时遇到了问题:

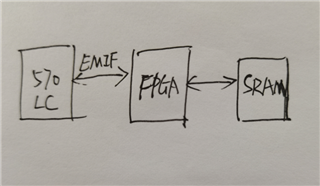

我们项目的背景是、TMS570LC4357通过 EMIF 总线连接到 FPGA、而 FPGA 连接到外部 SRAM。 TMS570LC4357通过 EMIF 总线操作 SRAM 以进行读取和写入。 现在已成功通过 TMS570LC4357操作 SRAM 的读取和写入函数。

现在、我想实现从 TMS570LC4357的片上闪存跳转到 SRAM 中运行的功能、但会始终发生预取中断错误。 关闭 MPU 后、再次出现 UNDEF 中断错误。

我们的具体操作程序如下:

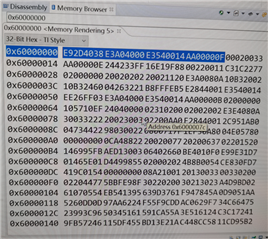

我编写了一个照明函数、使 LED 灯闪烁。 该函数被称为 FLASHTORAM。 然后编译整个项目、生成一个十六进制文件、并使用内存浏览器工具在十六进制文件中查找 FLASHTORAM 函数的所有内容。 然后、通过 EMIF 的 CS2芯片选择将此内容写入 SRAM。 写入地址为0x6000 0000。 最后、使用函数指针指向0x6000 0000。 您希望程序跳转到该地址并运行以实现 SRAM 中的照明效果。 停止。

跳转函数为:

空跳线地址(UINT32地址)

{

UINT32传输地址= 0;

TransferAddress =地址;

((void(*)(void))TransferAddress)();

}

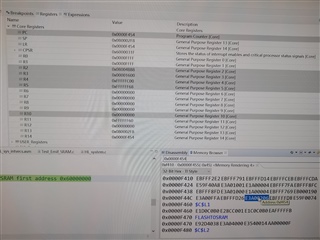

但每次运行跳转时、都会发生预取中断错误。 通过查看 cp15_instruction_fault_addrss 寄存器、我们发现错误地址为0x6000 0000。 我现在应该做些什么并解决问题?

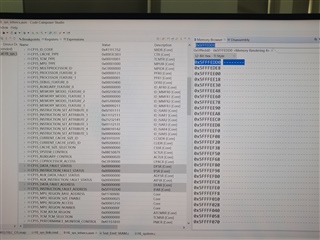

这是我们的 cmd 文件、它配置正确吗? 需要进行哪些更改? 使用 CS2片选地址、0x6000 0000、长度为0x0300 0000

这是我们的 cmd 文件、它配置正确吗? 需要进行哪些更改? 使用 CS2片选地址、0x6000 0000、长度为0x0300 0000

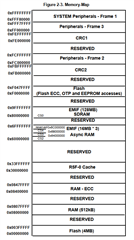

IFAR = 0x5FFFEDD0,且该地址没有代码。

IFAR = 0x5FFFEDD0,且该地址没有代码。  地址0x5FFFEDD0保留。

地址0x5FFFEDD0保留。