主题中讨论的其他器件: LP-AM243、 SysConfig

您好!所有 TI 专家!

我目前使用的是我们公司生产的产品电路板、以 AM2431作为主 IC。 我们的主板通过 RGMII 接口将 AM2431连接到 Realtek 以太网交换机 IC。 我们在与开关 IC 通信时会遇到问题。

我之前已在 LP-AM243开发板上测试了 SDK 中的"Enet 第2层 CPSW 示例"、并成功使其正常工作。 但是、LP 开发板使用 CPSW3G 配置一个主机端口和两个 MAC 端口、通过 MDIO/MDC 从外部连接到两个 PHY。 另一方面、我们的产品板仅连接到单个开关 IC、即一个 PHY。 因此、我认为应该将其配置为 CPSW2G、这意味着一个主机端口和一个 MAC 端口。 此外、我的开关 IC 需要通过 MDIO/MDC 接口进行初始化。 以下是我的问题:

- 在 SysConfig 中的 Enet (CPSW)-> Pinmux config 下、由于我只连接一个开关 IC、因此只需要一个 PHY。 这是否意味着我应该禁用 RGMII2的信号并仅保留 RGMII1?

- 我只需要一个 MAC 端口、因此应在 SysConfig 中的 Enet (CPSW)-> MAC Port Config -> MAC Port2 Config (MAC 端口2配置)下选择"禁用 Mac 端口2"?

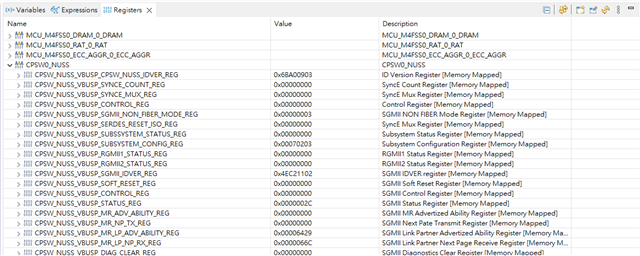

- 根据 SDK 文档,特别是"Networking->Enet-LLD->Ethernet PHY Integration Guide"和"Networking->Enet-LLD->Enet Migration Guide",我需要在相应的地址为交换机 IC 创建 PHY 驱动程序。 我还创建了 custom_board_config.c 文件、选中 sysconfig 中 Enet (CPSW)->Board Config 下的选项。 但是、PHY 仍然无法连接。 我的代码主要是对"Enet Layer 2 CPSW 示例"的修改。 日志在执行"cpsw-3g: Waiting for link up..."后停止。 我怀疑这可能是因为我的开关 IC 未在初始化过程中、因为我没有看到程序执行我编写的 Phy 驱动程序。 即使在调试模式下、我也无法看到程序到达对应器件、这让我无法确定器件上是否存在配置错误。

有人能指导我做哪些修改吗?或者我可以参考其他文档吗?

此致、

拉里