大家好、

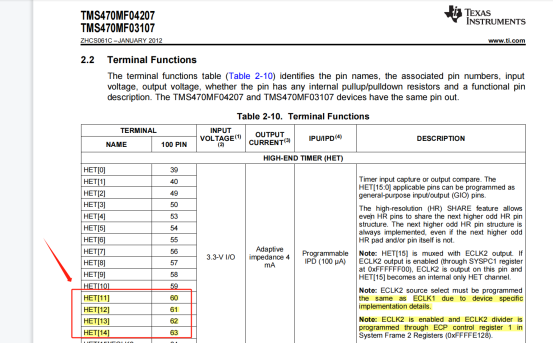

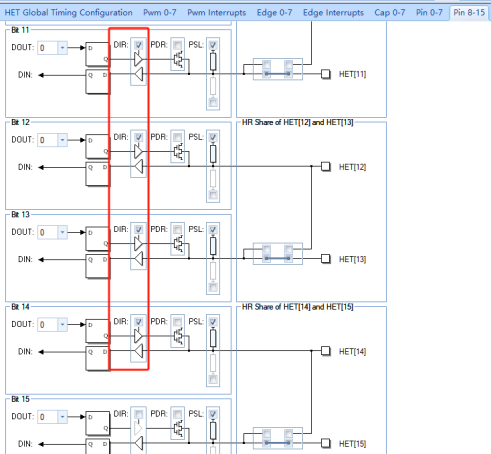

tms470mf03107 HET 模块引脚说明:

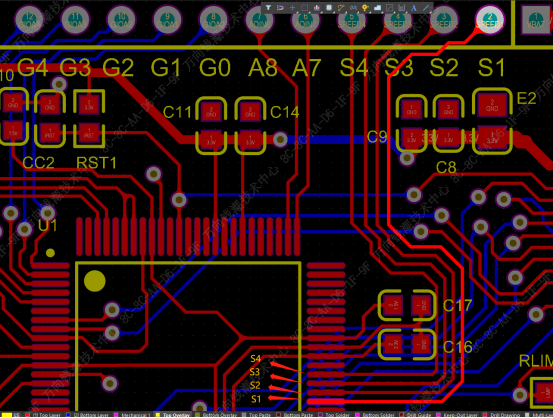

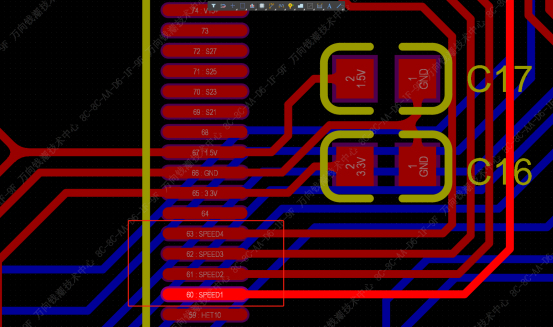

PCB 4 PWM 引脚布局:

放大后:

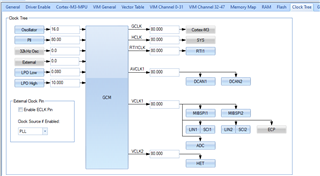

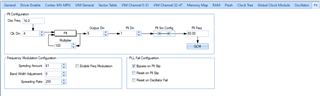

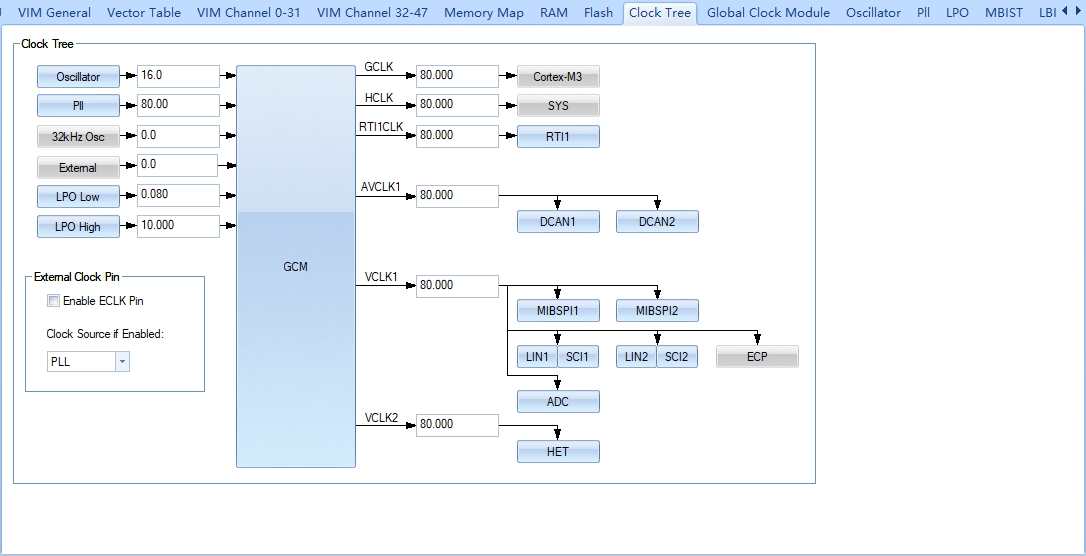

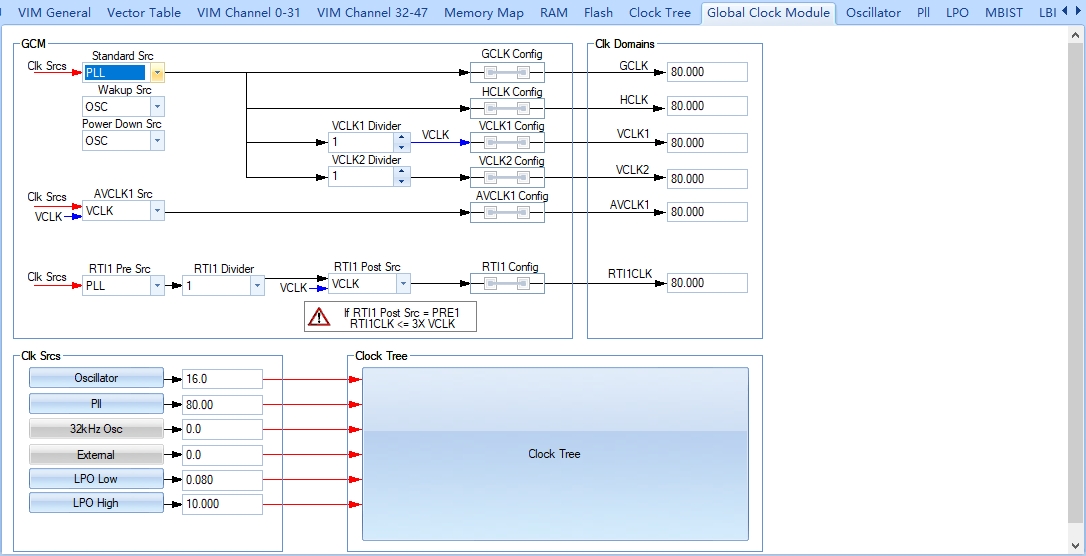

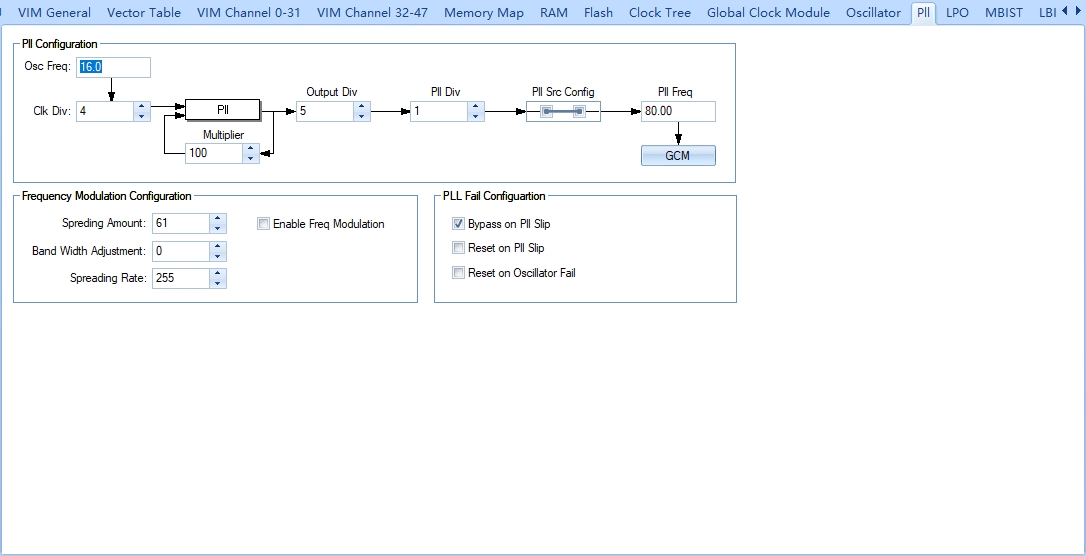

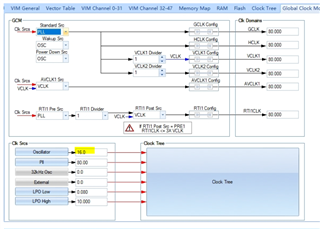

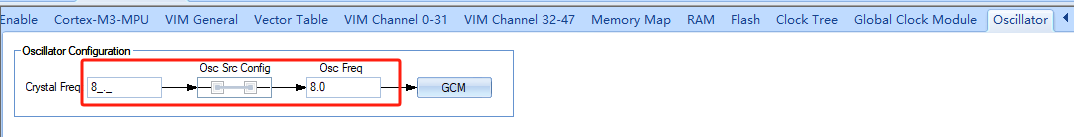

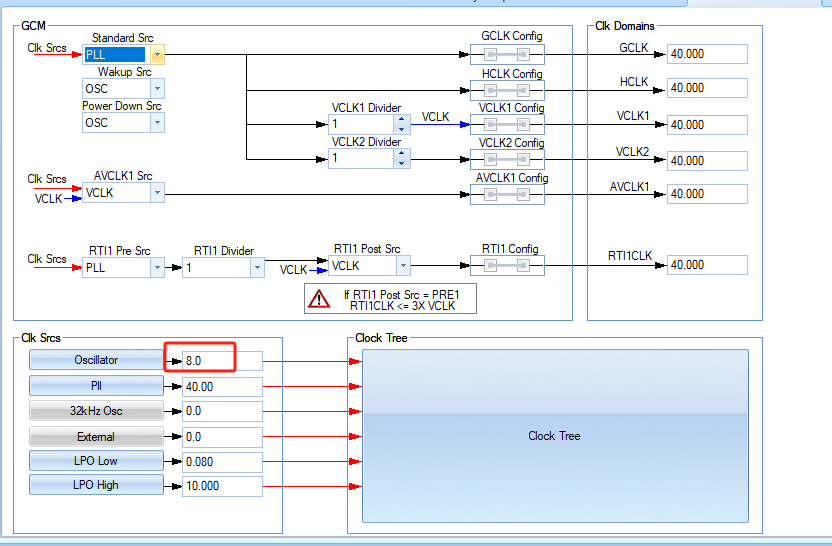

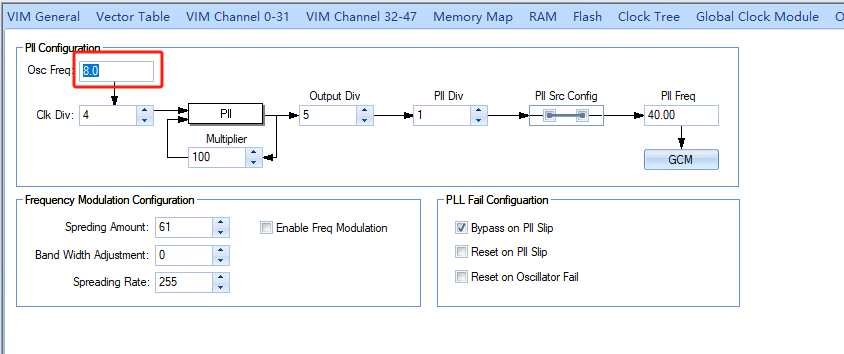

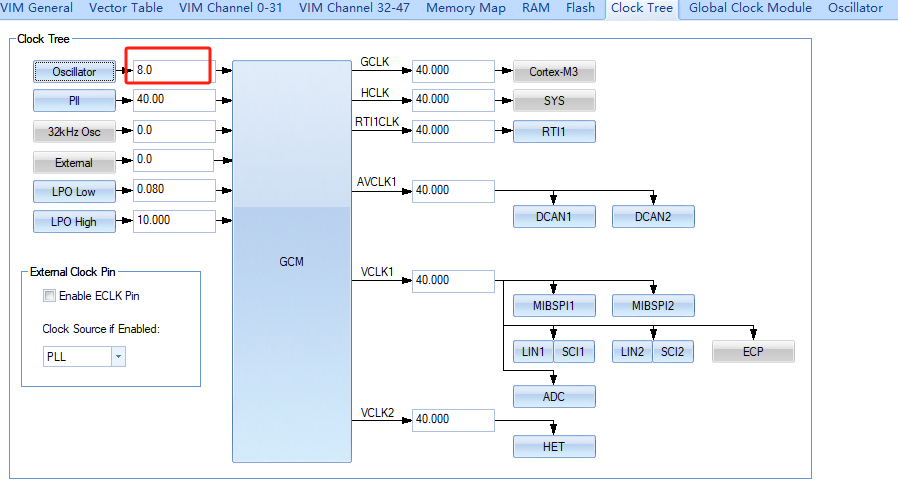

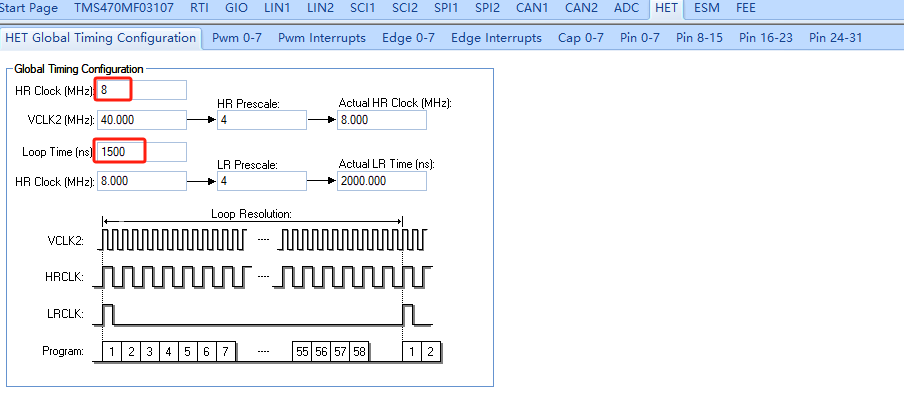

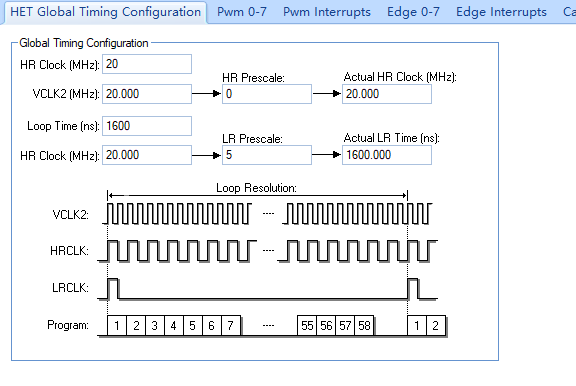

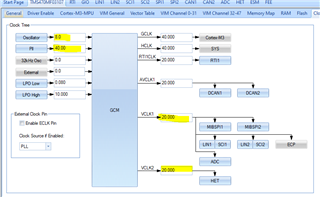

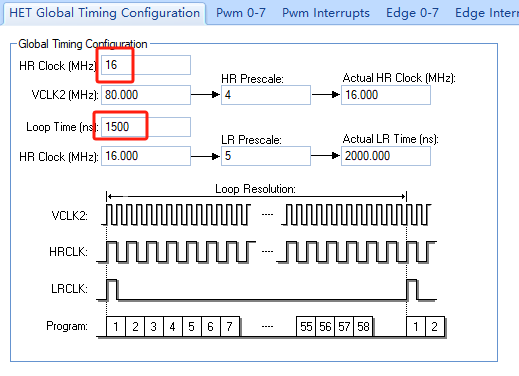

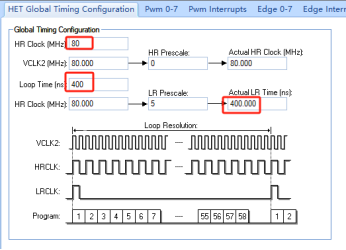

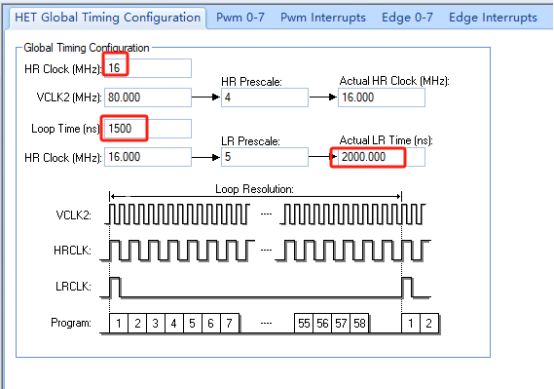

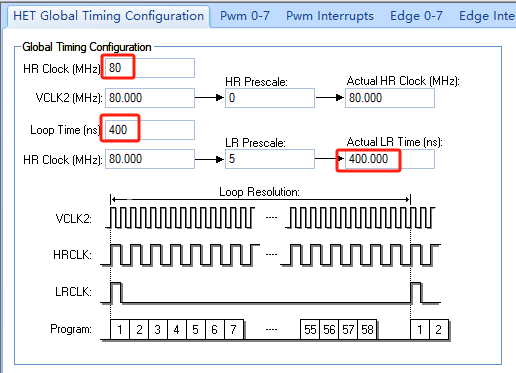

HET 全局时序配置如下:

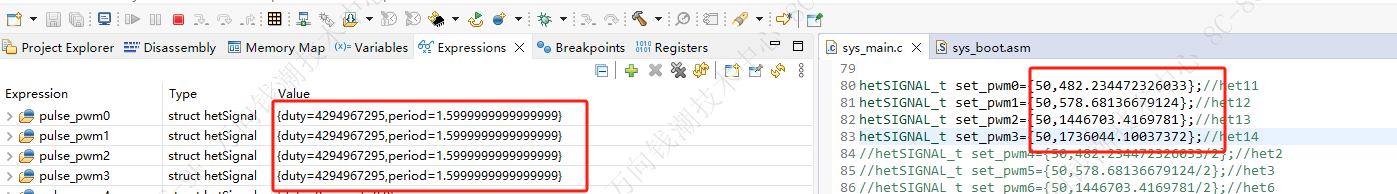

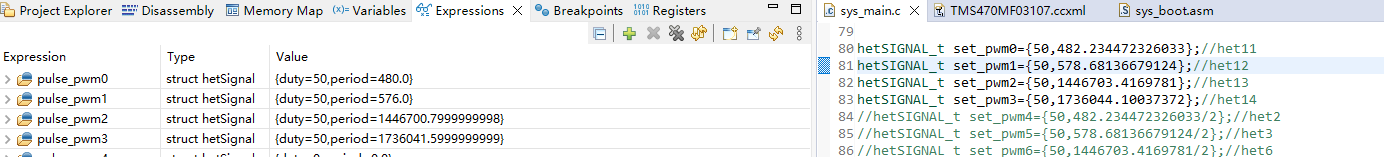

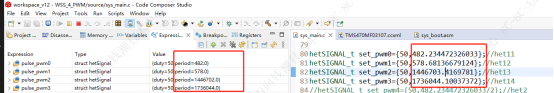

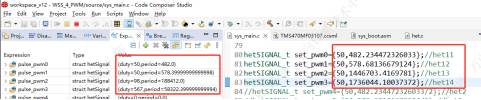

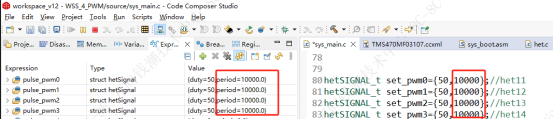

主函数如下:

int main (空)

{

/*用户代码开始(2)*/

hetInit ();

pwmSetSignal (pwm0、set_pwm0);

pwmSetSignal (pwm1、set_pwm1);

pwmSetSignal (pwm2、set_pwm2);

pwmSetSignal (pwm3、set_pwm3);

// pwmSetSignal (pwm4、set_pwm4);

// pwmSetSignal (pwm5、set_pwm5);

// pwmSetSignal (pwm6、set_pwm6);

// pwmSetSignal (pwm7、set_pwm7);

pwmStart (pwm0);

pwmStart (pwm1);

pwmStart (pwm2);

pwmStart (pwm3);

// pwmStart (pwm4);

// pwmStart (pwm5);

// pwmStart (pwm6);

// pwmStart (pwm7);

PULSE_pwm0 = pwmGetSignal (pwm0);

PULSE_pwm1 = pwmGetSignal (pwm1);

pulse_pwm2 = pwmGetSignal (pwm2);

pulse_pwm3 = pwmGetSignal (pwm3);

// pulse_pwm4 = pwmGetSignal (pwm4);

// pulse_pwm5 = pwmGetSignal (pwm5);

// pulse_pwm6 = pwmGetSignal (pwm6);

// pulse_pwm7 = pwmGetSignal (pwm7);

// }

/*用户代码结束*/

}

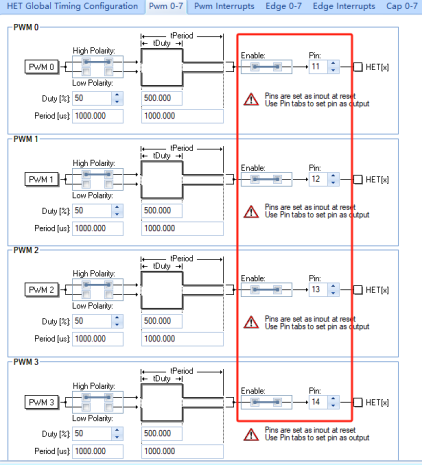

4 PWM 信号周期设置与程序生成的 PWM 信号相同、涵盖我需要的最小(482us)和最大周期(1736044us)。

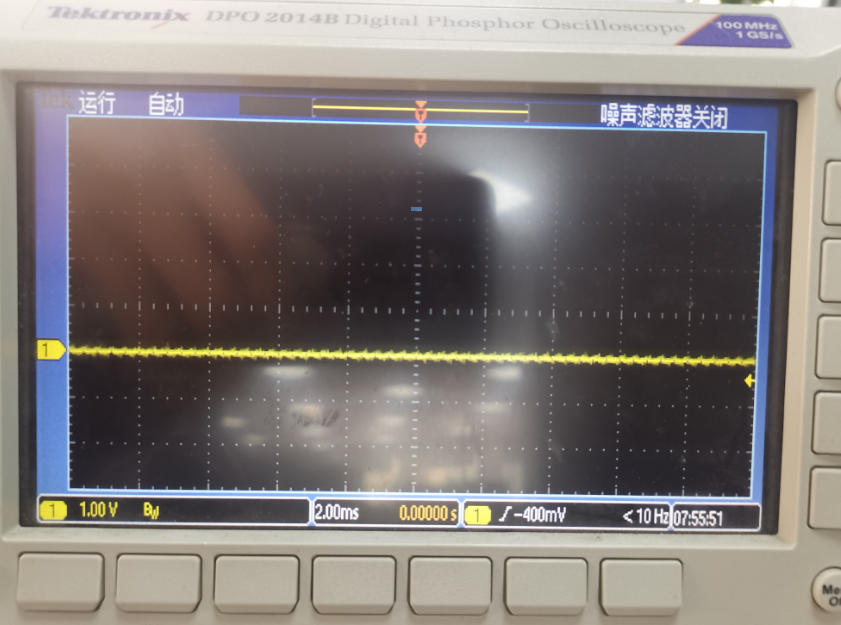

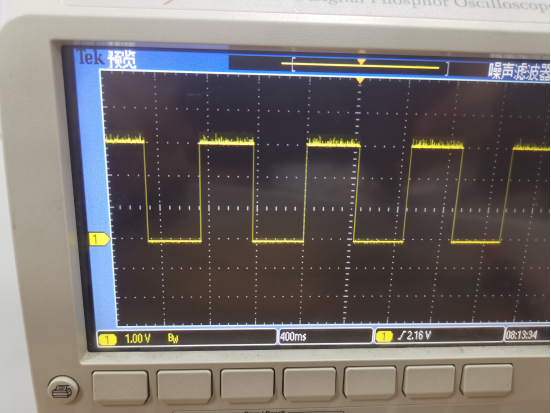

但实际的 PWM 信号波如下:

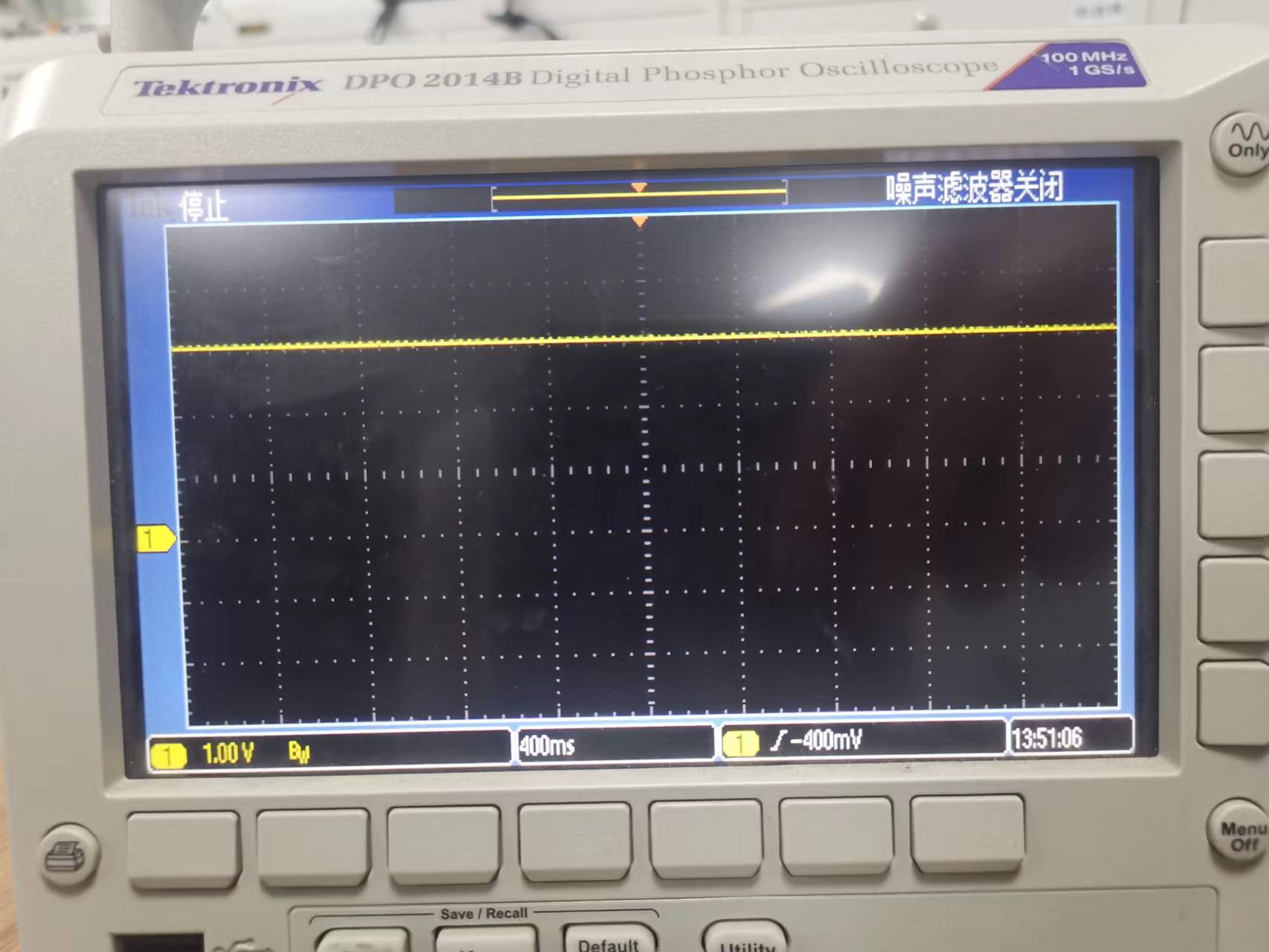

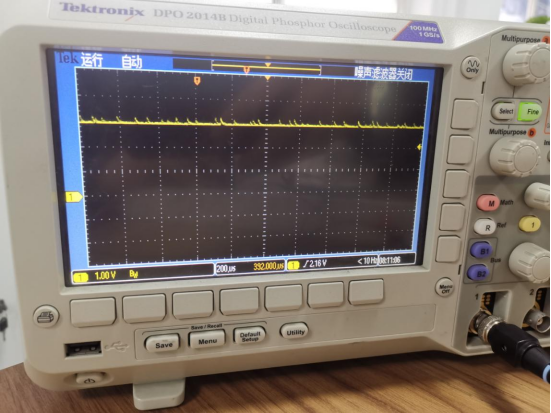

S1 (PWM0、HET[11]):

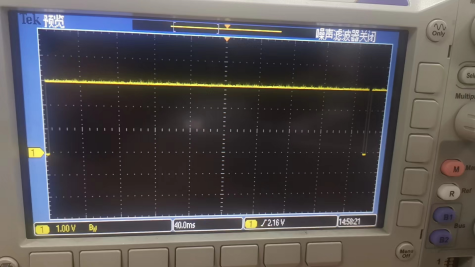

持续高电平:

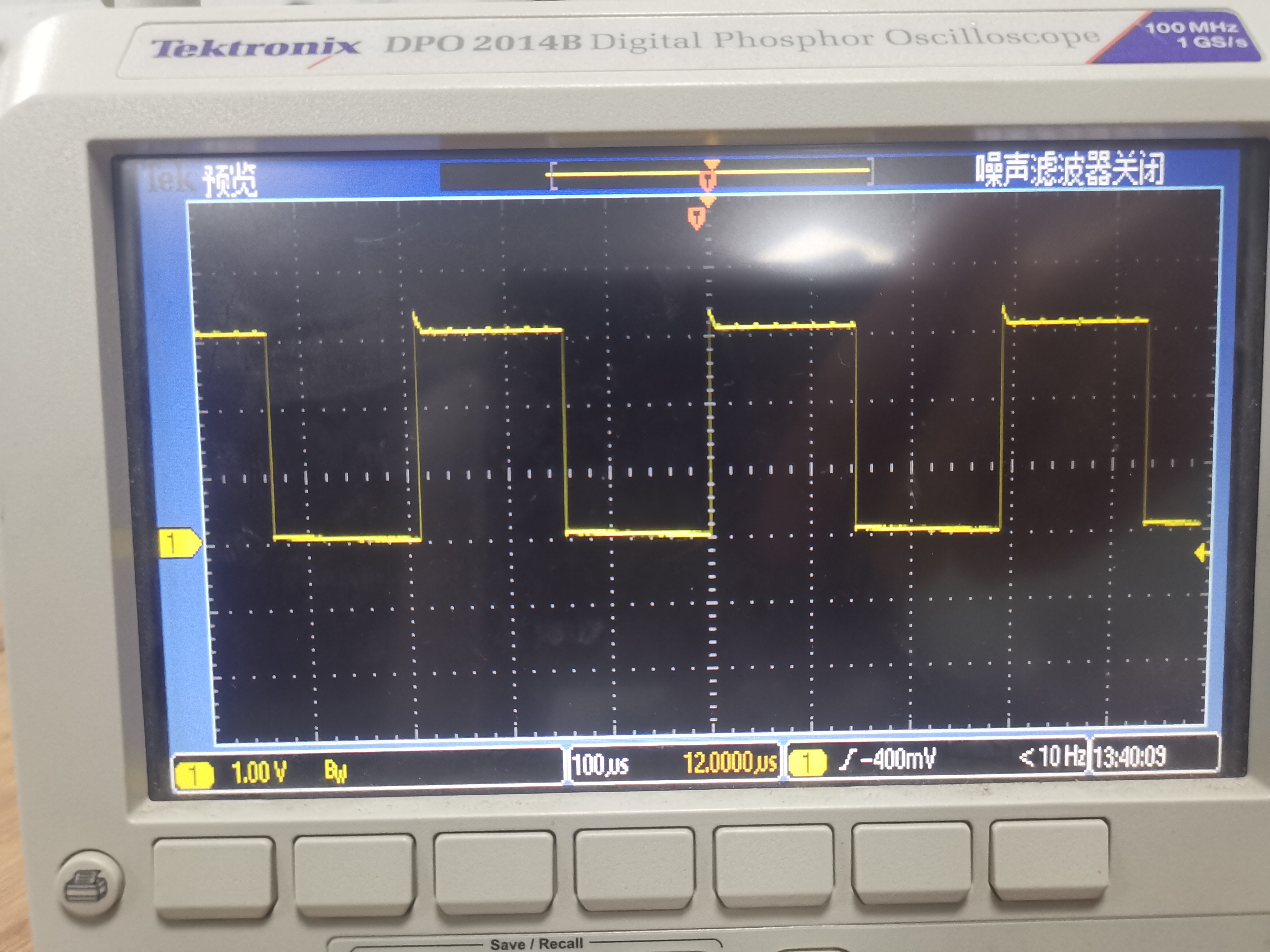

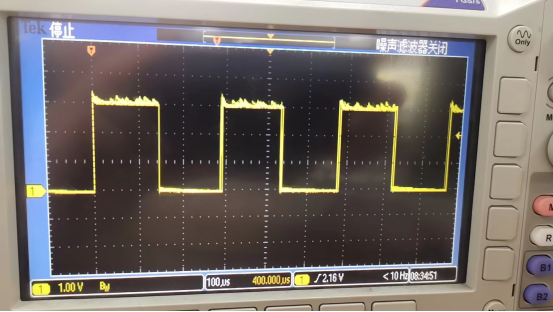

S2 (PWM1、HET[12]):

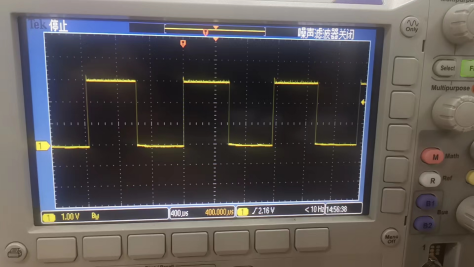

,的 PWM 波形:周期为290us μ s、即设定周期578us 的一半

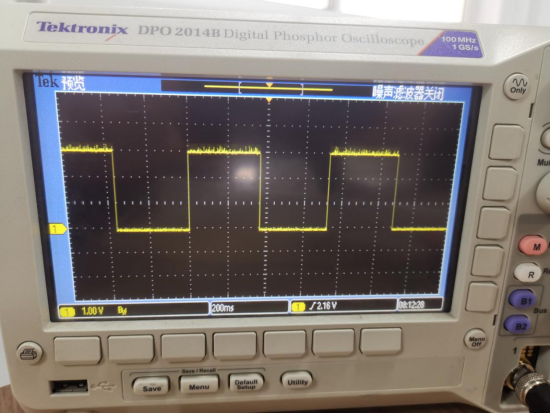

:(pwm2, het[13])

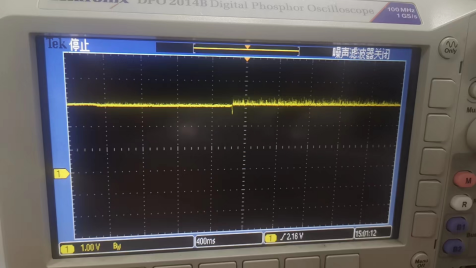

显示的 PWM 波形输出周期为720ms,、相当于设定周期1446703us:的一半

S4 (PWM3、HET[14]):

显示的 PWM 波形输出周期为880ms,、为设定周期1736044us 的一半

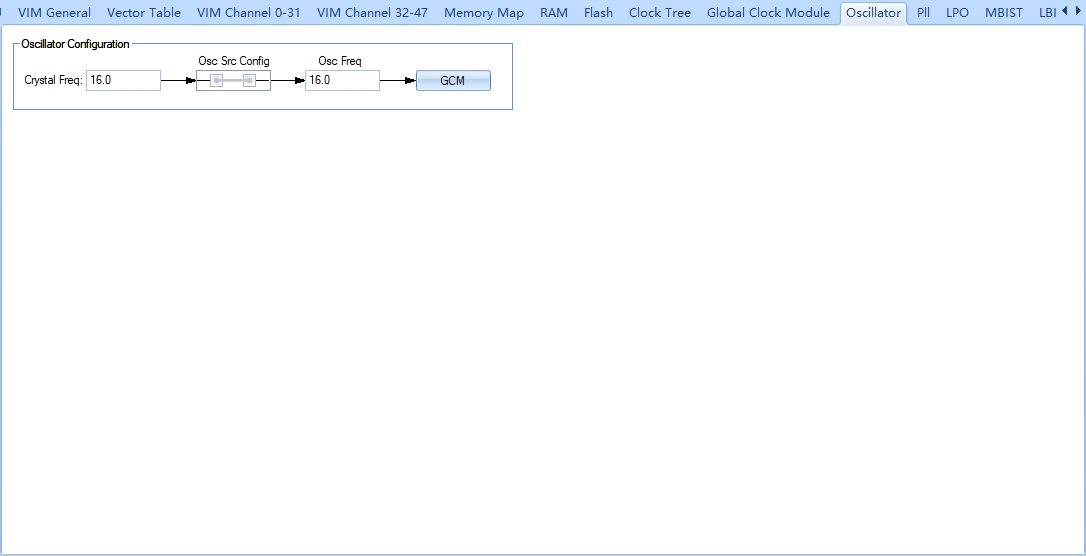

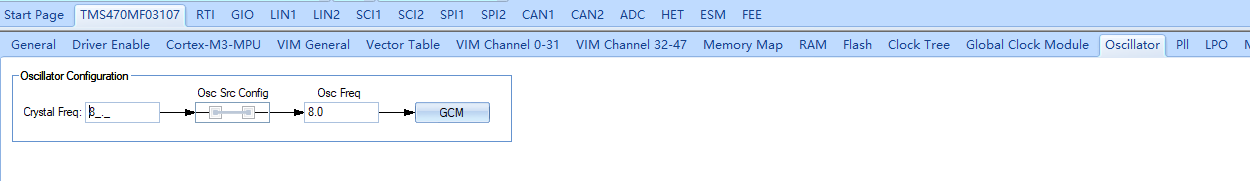

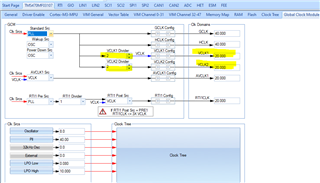

当全局时序配置如下所示时、它是默认设置( 其他配置保持不变 ):

PWM0和 PWM1周期设置与程序生成的值相同、但 PWM2和 PWM3占空比和周期的程序生成值与设置的占空比和周期相比异常。 您可以看到以下内容:

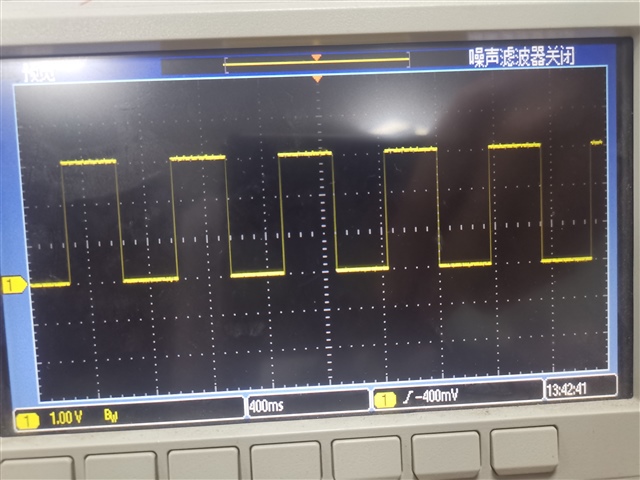

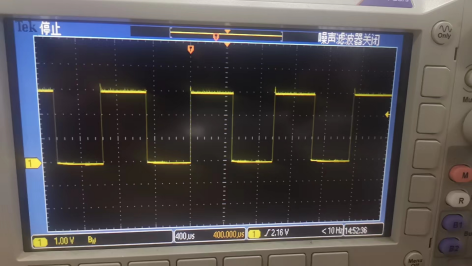

示波器屏幕显示如下:

S1:period=960us、设定周期的两倍480us

S2:period=1160us、如果设定的周期578us 则两次

S3:几乎恒定电平376ms、是188414us 的两倍

S4:占空比异常、恒定高电平:

此处、为了简化、其他一些测试和描述如下:

HET 全局时序配置一:

4个 PWM 信号周期的设置是10000us (10ms)、与生成的 PWM 信号相同:

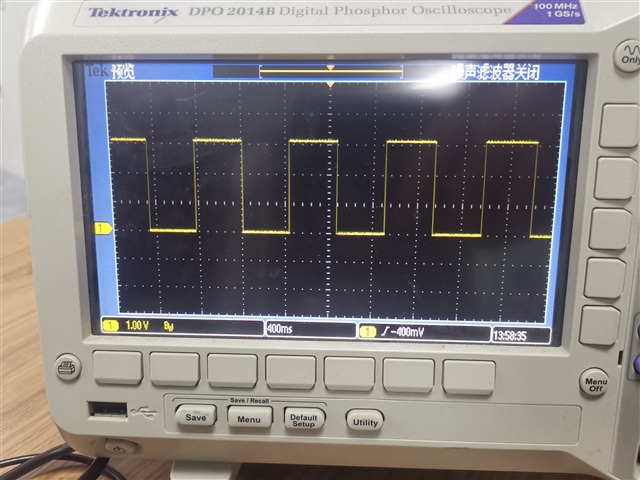

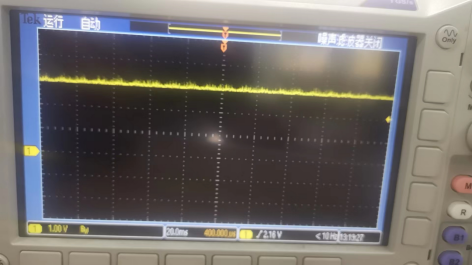

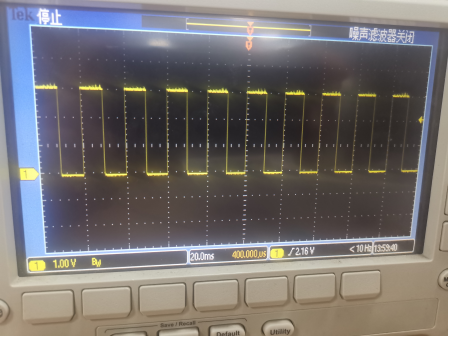

但实际的 PWM 脉冲波如下:

S1(PWM0,HET[11]):示波器屏幕上没有显示 PWM 波形,但一直拉高。

S2 (PWM1,HET[12]),S3 (PWM2,HET[13]),S4(PWM3,HET[14]):PWM 波在屏幕上显示如下,但脉冲周期(5000us 或5ms)是设定周期的一半(10000us 或10ms):

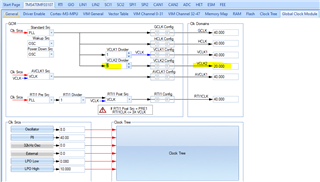

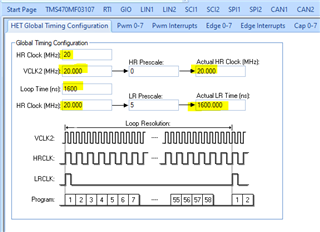

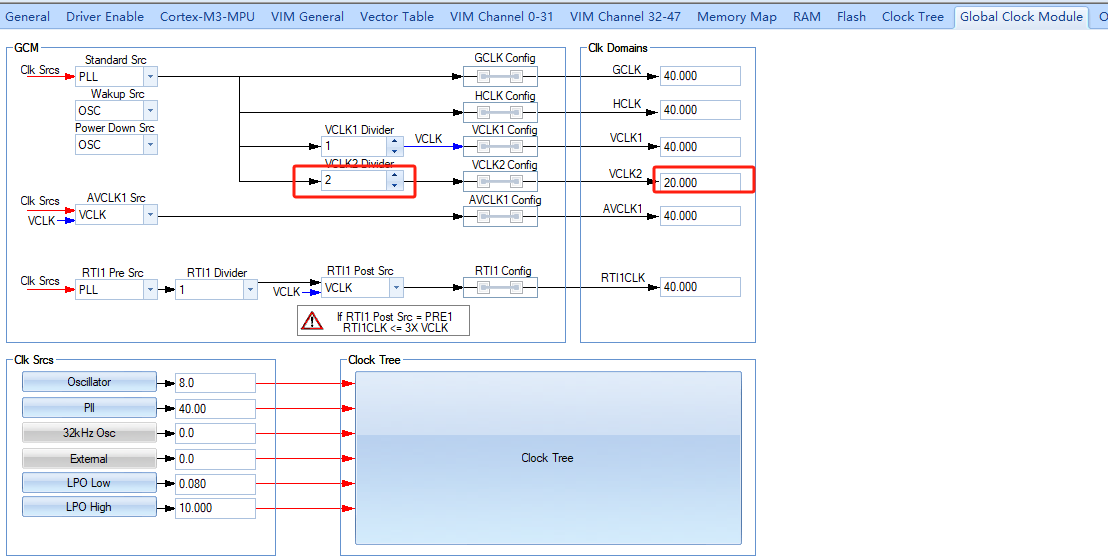

当全局时序配置2如下所示时:

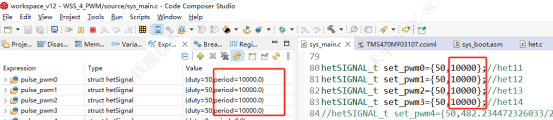

4个 PWM 信号周期的设置是10000us (10ms)、与生成的 PWM 信号相同:

但实际的4 PWM 脉冲波是如下,显然都有高和低电平,但脉冲周期(20000us 或20ms)是设置周期(10000us 或10ms)的两倍。

,、我想、基于特定的 HET 时序配置、为什么生成的 PWM 周期与 我设置的 PWM 周期(和占空比)不同?

您能帮助检查这个问题吗? 谢谢。

此致、

切里