您好!

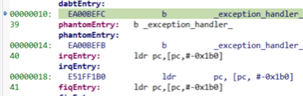

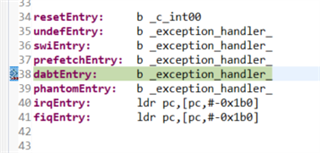

我在汇编中编写了一个异常处理程序、它分支到异常之后。

在上下文中、数据中止作为启动自检例程的一部分生成。 在这些数据中止期间、 会发生以下事件之一、具体取决于_exception_handler_的位置:

- 成功分支到_exception_handle_。

- PC 不会分支到_exception_handler_、而是递增到下一条指令(phantomEntry)。 此时、调试工作变得不可预测(nRST 会导致重置为随机位置-不是0x0、"恢复"操作会导致"步进"操作等)

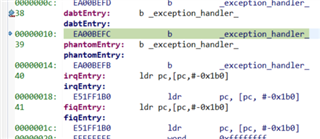

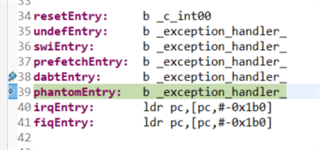

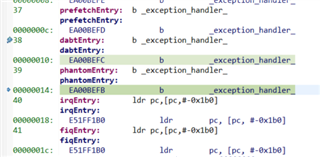

请注意在故障情况下捕获的以下屏幕截图。

A)抛出数据中止。

b) 在"汇编步骤进入"操作后、PC 递增到下一条指令、而不分支到_except_handle_。

记录的成功/失败案例如下所示:

| 异常处理程序_地址 | 测试结果 |

| 0x2FB98 | 失败 |

| 0x2FB9C | 失败 |

| 0x2FBA0 | 失败 |

| 0x2FC10 | 失败 |

| 0x2FC0C | 失败 |

| 0x2FC08 | 失败 |

| 0x2FC18 | 通过 |

| 0x2FC1C | 通过 |

| 0x2FC20 | 通过 |

| 0x2FC28 | 通过 |

| 0x2FC2C | 通过 |

| 0x2FC30 | 通过 |

| 0x2FC88 | 通过 |

| 0x30B08 | 通过 |

此外、我已经 通过内存浏览器以及输出.bin 文件在失败和成功情况下验证分支指令是正确的。

非常感谢您提供任何输入。

谢谢。

格雷森