主题中讨论的其他器件:HALCOGEN

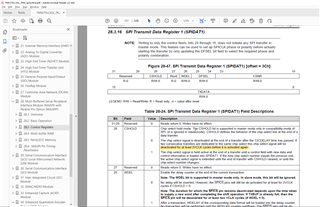

我当前使用 SPI1进行一些通信。 在我写入缓冲区时、我要与之对话的器件需要 CS 保持有效状态(低电平)。 但是、使用 DMA 似乎失去了控制 SPI CS 保持的能力。 在每次发送缓冲区并保持 CS 处于活动状态之前、我必须稍微修改 halcogen 代码、以便可以发送特定的3个字节。

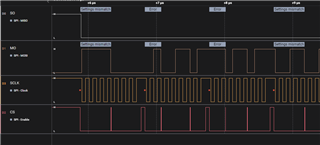

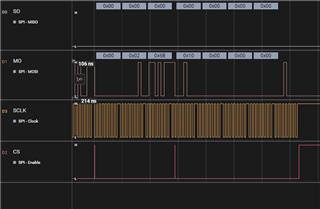

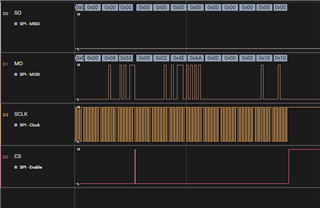

在下图中、显示了每次8位传输后 CS 线路的切换、这就是我要防止的情况。 其他一切似乎都正常。

只是我希望 CS 线路在整个 DMA 传输期间保持低电平有效。 以下是我的问题:

1.是否有办法使用 CS 的 SPI 模式引脚和 DMA 来控制 CS 在整个块传输期间保持低电平? 或者我是必须改用 GIO 引脚吗?

2.切换到 mibSPI 是否是更好的选择? 这是否通过 DMA 提供对 CS 引脚的更多控制?