主题中讨论的其他器件: AM2631

您好、TI 专家、

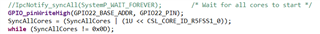

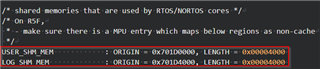

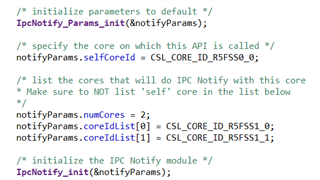

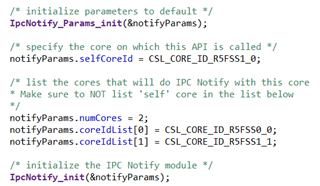

我正在用户共享存储器区域(地址0x701D0000)中使用一个全局变量、该变量由多个内核位屏蔽。

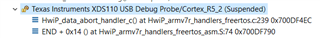

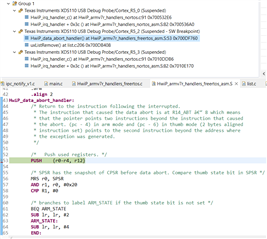

有时在无引导模式下运行时、我观察到地址 0x701D0000处的变量会被不同内核而不是位屏蔽覆盖。 特别是、当我将应用软件刷写到 QSPI 闪存中时、应用软件不会启动、因为我认为执行会卡住、检查位屏蔽变量是否为指定值。

您能告诉我如何解决此问题吗? 是否有 MPU 设置可以阻止对其他内核进行存储器覆盖? RAM/缓存或引导加载程序中需要进行哪些更改?

提前感谢!