主题中讨论的其他器件:AM2634、 SysConfig

您好

我们设计了 MCU (AM2634)+PMIC (TPS653850)板、但当我将最终设计中的所有 GPIO (大约84个 GPIO)添加到"hello world"示例代码时、我遇到了启动问题。

问题说明:

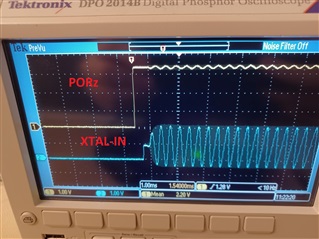

- 我使用了来自"AM263x MCU+ SDK 09.00.00 "的"hello_world_am263x-cc_r5fss0-0_freertos_ti-arm-clang"示例作为基础软件、并在 SYSCfg 文件中添加了84个 GPIO。 这84个 IO 中只有一个用作 LED、其余83个 IO 仅在 SysConfig 生成的文件中进行初始化、从不在主代码中使用。

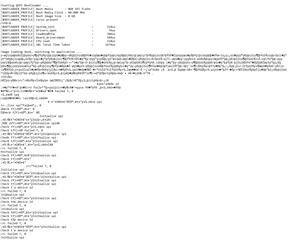

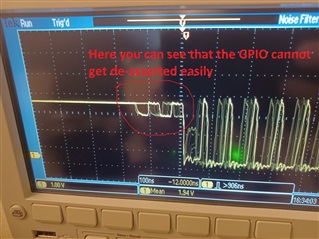

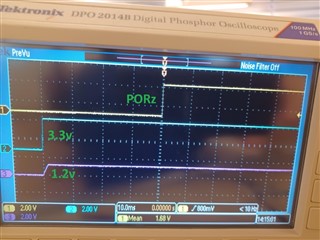

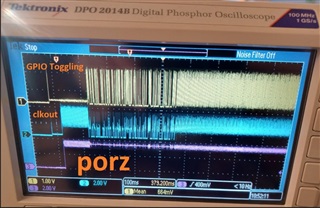

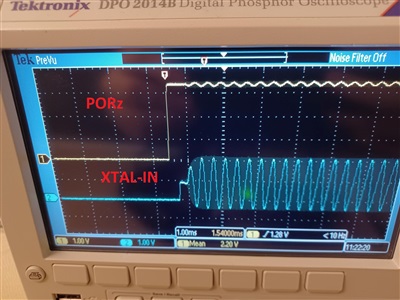

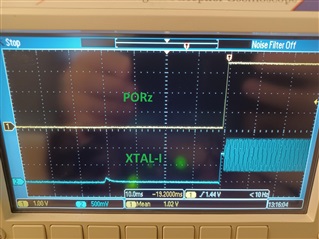

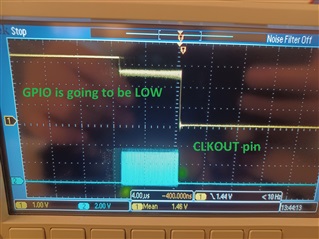

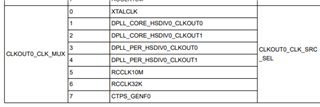

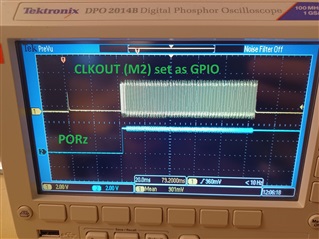

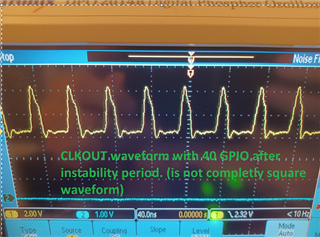

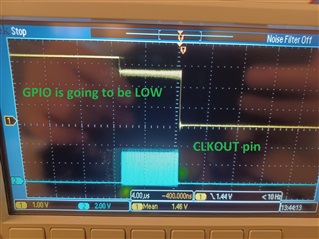

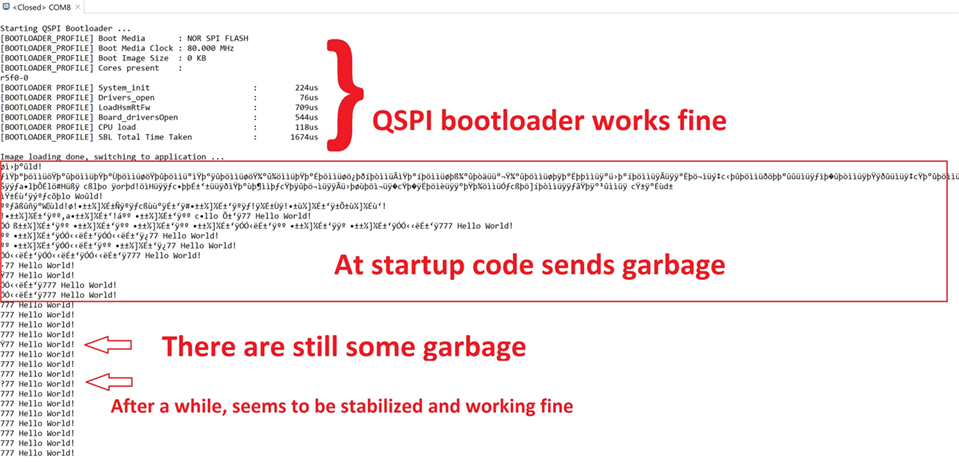

- 当电路板在关闭一段时间后加电、MCU 会向 UART 控制台发送垃圾数据、修复需要一段时间(大约15秒)、并且 UART 上会接收到正常数据、就会出现这个问题。 稳定后、如果电路板在没有明显延迟的情况下关闭并再次加电、它将正常工作。 否则,如果它关闭了很长的时间车库又来了。

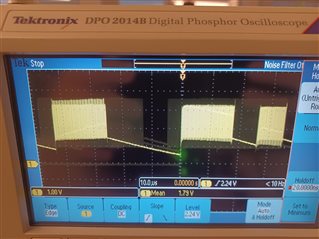

不稳定性期间的 UART TX 数据

- 关闭的持续时间与试验板稳定和运转良好所需的时间有直接关系。

- 值得一提的是、在 AM263x 控制卡 EVM 中、同样的代码可完全正常工作。