主题中讨论的其他器件:AM4376、 ISO7242M

我正尝试使用具有可编程实时单元的8b-10b 线路代码来评估内部驱动器通信-应用手册。 是否会提供源代码文件? 这样可以节省大量时间、并为如何正确使用 PRU 提供一个很好的示例。

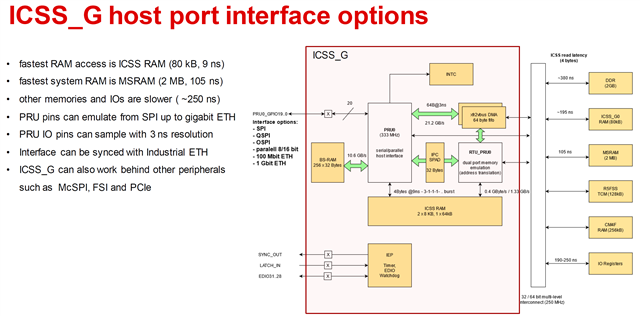

我还一直在查看 AM243x Launch_Pad 的示例、但没有 PRU 示例。 通过共享 RAM 与 R5F 内核连接的 PRU 示例的最佳资源是什么?

最终、我将要在两个 MCU 之间创建一个高串行链路、从 R5F 的角度来看、这基本上是一个无驱动的链路。