请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TM4C1290NCPDT 我们有一个30.72Mhz 的外部时钟输入到 TMC4、我们将该时钟输出到一个 FPGA 和几个二阶加速器。 双 ART 是异步的、但会将时钟馈送到 FPGA 中、以使其与 TM4C 同步。 如果可能、我们不想更改 FPGA 代码、因此我们正在尝试合成测试模型、看看读取和写入是否可行。 我们需要知道/了解 EPI 时钟与读写线之间的时序关系。

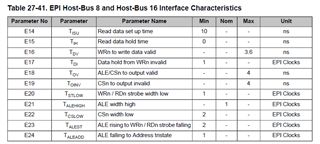

对于主机16 EPI 模式(是异步模式)、/RD 和/Write 的设置和保持时间与系统时钟的关系是什么?