您好!

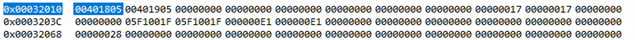

我正在尝试在 PRU 上编写自己的开关实现。 为此、我编写了汇编程序代码来测试通过以太网发送和接收数据。 接收正常、但我无法让 PRU 发送数据。 我使用 L1 FIFO 和 R30/R31接口的两种方式。 在寄存器0x300B 2068中、我可以清楚地看到 FIFO 充满、但永远不会变为空。 我在填充 FIFO 后已尝试手动设置 TX_ENABLE、但 TX_EN 似乎从未被置位。

从参考手册中我了解到、当满足以下条件时会自动设置 TX_EN:

TX L1 FIFO 不为空

2.数据包间隙(IPG)计时器过期

3. RX_DV 至 TX_EN 计时器过期

4. TX_EN 比较计时器过期

据我所知、所有这些要求都得到了满足、所以我不知道 FIFO 为什么没有被清空。

那么、以下几个问题可能会让我更进一步解决我的问题:

1.向 MII 发送数据的最低要求是什么? 我是否需要发送有效帧、或者0xFF 的一些字节是否仍会被进一步处理? 我是否需要配置 MAC 和 MDIO?

2、如果设置了 RX_DV 或 TX_EN、我可以从哪里读取? 从何处可以看到上面命名的计时器是否已过期?

此外,在我的研究期间,我发现这在参考手册第3261页:

4.11.2.4.1.1.4.1 TX 抢占编程模型

开始新的帧。

1.等待发生 R31.TX_EOF 事件

2.将数据载入 TX L2 FIFO 直到整个帧结束

3。发出 R30.TX_EOF + TX_CRC_HIGH + TX_CRC_LOW

它不应该是 R31而不是 R30?

提前感谢您的回答。

此致

让徒玛丽亚斯