主题中讨论的其他器件:HALCOGEN

您好!

我 正在尝试在 Halcogen/CCS 项目中使用 SPI5 RX 中断、

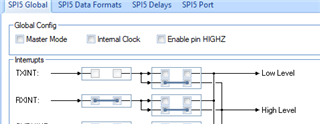

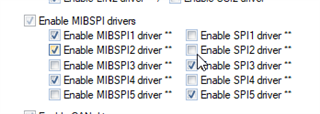

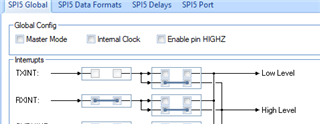

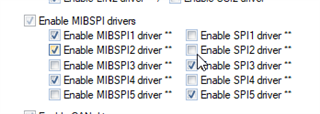

SPI 5未处于 MibSPi 模式:

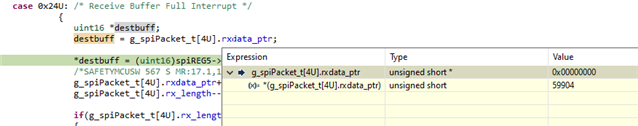

中断例程被调用:

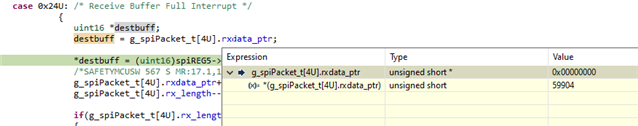

此处、程序崩溃、因为它使用了一个 NULL 指针。 这似乎与 MibSpi 有关、为什么生成和调用该无效代码?

如果项目有所帮助、我会将其附加到项目中。

此致

于尔根

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我 正在尝试在 Halcogen/CCS 项目中使用 SPI5 RX 中断、

SPI 5未处于 MibSPi 模式:

中断例程被调用:

此处、程序崩溃、因为它使用了一个 NULL 指针。 这似乎与 MibSpi 有关、为什么生成和调用该无效代码?

如果项目有所帮助、我会将其附加到项目中。

此致

于尔根

尊敬的 Juergen:

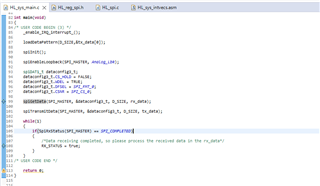

如果您启用 SPI Rx 中断、那么在发送数据之前、您应该使用"spiGetData"函数调用并初始化目标缓冲区。

例如、您可以看到以下代码:

在此代码中、我只调用了"spiGetData"函数、并初始化 要接收的目标缓冲区和块大小。

完成此操作后、您可以调用"SpiRxStatus"函数来检查接收状态。

我在此附上我的示例代码、请将其作为参考并进行必要的修改。

e2e.ti.com/.../SPI_5F00_Rx_5F00_Interrupt_5F00_Test_5F00_LC4357.zip

--

谢谢。此致、

Jagadish。

Jagadish、您好!

感谢您的帮助、它很有效。 现在我要尝试使用 SPI 和 DMA。 SPI3是主器件、SPI5是从器件。 在示波器上、我可以看到 DMA 必须触发传输、因为 SPI3输出时钟信号且 CS 变为低电平。 但是 SIMO 线保持低位、我不明白为什么。 下面是我的代码:

#define SPI_MASTER_TX_SIZE 5

uint32_t mTxDat[SPI_MASTER_TX_SIZE] = {

0x103EA1A2, // FMT = 0, CS=CS0, HOLD=1, Data = 0xA1A2

0x103EA3A4, // FMT = 0, CS=CS0, HOLD=1, Data = 0xA3A4

0x103EA5A6, // FMT = 0, CS=CS0, HOLD=1, Data = 0xA5A6

0x103EA7A8, // FMT = 0, CS=CS0, HOLD=1, Data = 0xA7A8

0x003EA9AA, // FMT = 0, CS=CS0, HOLD=0, Data = 0xA9AA

};

uint16_t sRxDat[SPI_MASTER_TX_SIZE];

g_dmaCTRL g_dmaCTRLPKT_SPI3_TX;

g_dmaCTRL g_dmaCTRLPKT_SPI5_RX;

#define DMA_SPI3_RX_CH DMA_CH14

#define DMA_SPI3_TX_CH DMA_CH15

#define DMA_SPI3_RX_REQ DMA_REQ14

#define DMA_SPI3_TX_REQ DMA_REQ15

#define DMA_SPI5_RX_CH DMA_CH30

#define DMA_SPI5_TX_CH DMA_CH31

#define DMA_SPI5_RX_REQ DMA_REQ30

#define DMA_SPI5_TX_REQ DMA_REQ31

int main(void)

{

spiInit();

spiREG3->INT0 &= ~0x0300U; /* DMA => turn off RX/TX ints */

spiREG5->INT0 &= ~0x0300U;

g_dmaCTRLPKT_SPI3_TX.SADD = (uint32)(&mTxDat); /* source address */

g_dmaCTRLPKT_SPI3_TX.DADD = (uint32)(&spiREG3->DAT1); /* destination address */

g_dmaCTRLPKT_SPI3_TX.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT_SPI3_TX.FRCNT = SPI_MASTER_TX_SIZE; /* frame count */

g_dmaCTRLPKT_SPI3_TX.ELCNT = 1; /* element count */

g_dmaCTRLPKT_SPI3_TX.ELDOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT_SPI3_TX.ELSOFFSET = 0; /* element source offset */

g_dmaCTRLPKT_SPI3_TX.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT_SPI3_TX.FRSOFFSET = 0; /* frame source offset */

g_dmaCTRLPKT_SPI3_TX.PORTASGN = PORTA_READ_PORTB_WRITE; /* rd from RAM, wr to periph */

g_dmaCTRLPKT_SPI3_TX.RDSIZE = ACCESS_32_BIT; /* read size */

g_dmaCTRLPKT_SPI3_TX.WRSIZE = ACCESS_32_BIT; /* write size */

g_dmaCTRLPKT_SPI3_TX.TTYPE = FRAME_TRANSFER; /* transfer type */

g_dmaCTRLPKT_SPI3_TX.ADDMODERD = ADDR_INC1; /* address mode read */

g_dmaCTRLPKT_SPI3_TX.ADDMODEWR = ADDR_FIXED; /* address mode write */

g_dmaCTRLPKT_SPI3_TX.AUTOINIT = AUTOINIT_OFF; /* autoinit */

g_dmaCTRLPKT_SPI5_RX.SADD = (uint32_t)((uint32)&(spiREG5->BUF) + 2); /* source address */

g_dmaCTRLPKT_SPI5_RX.DADD = (uint32)(&sRxDat); /* destination address */

g_dmaCTRLPKT_SPI5_RX.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT_SPI5_RX.FRCNT = SPI_MASTER_TX_SIZE; /* frame count */

g_dmaCTRLPKT_SPI5_RX.ELCNT = 1; /* element count */

g_dmaCTRLPKT_SPI5_RX.ELDOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT_SPI5_RX.ELSOFFSET = 0; /* element source offset */

g_dmaCTRLPKT_SPI5_RX.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT_SPI5_RX.FRSOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT_SPI5_RX.PORTASGN = PORTB_READ_PORTA_WRITE; /* red from periph, wr to RAM */

g_dmaCTRLPKT_SPI5_RX.RDSIZE = ACCESS_16_BIT; /* read size */

g_dmaCTRLPKT_SPI5_RX.WRSIZE = ACCESS_16_BIT; /* write size */

g_dmaCTRLPKT_SPI5_RX.TTYPE = FRAME_TRANSFER ; /* transfer type */

g_dmaCTRLPKT_SPI5_RX.ADDMODERD = ADDR_FIXED; /* address mode read */

g_dmaCTRLPKT_SPI5_RX.ADDMODEWR = ADDR_INC1; /* address mode write */

g_dmaCTRLPKT_SPI5_RX.AUTOINIT = AUTOINIT_OFF; /* autoinit */

dmaSetCtrlPacket(DMA_SPI3_TX_CH, g_dmaCTRLPKT_SPI3_TX);

dmaReqAssign(DMA_SPI3_TX_CH, DMA_SPI3_TX_REQ );

dmaSetChEnable(DMA_SPI3_TX_CH, DMA_HW);

dmaSetCtrlPacket(DMA_SPI5_RX_CH, g_dmaCTRLPKT_SPI5_RX);

dmaReqAssign(DMA_SPI5_RX_CH, DMA_SPI5_RX_REQ);

dmaSetChEnable(DMA_SPI5_RX_CH, DMA_HW);

spiREG5->INT0 |= 0x00010000; /* DMA REQ EN */

dmaEnable();

/* DMA REQ EN => kicks off 1st DMA transfer when SPI is enabled */

spiREG3->INT0 = (spiREG3->INT0 & 0x0000FFFFU) | 0x00010000;

}

这是 CCS 项目:

您好、Ju_We:

e2e.ti.com/.../0878.SPI_5F00_DMA_5F00_TEST_5F00_LC4357.zip

e2e.ti.com/.../0878.SPI_5F00_DMA_5F00_TEST_5F00_LC4357.zip

此处是几个 DMA 示例、请将其作为参考并进行必要的修改。

如果上述线程最终无法解决问题、那么您可以在 SPI 中针对此 DMA 问题提出一个新线程吗?

--

谢谢。此致、

Jagadish。