你(们)好!

我想知道是否能完全禁用 Hercules 上的所有中断、包括 FIQ。

根据 spna218部分2.5、一旦启用、FIQ 便无法禁用。 但是、我们需要一个完全不能中断的严重错误处理程序。

我 已经使用 CPSID AIF 指令禁用其它中断、但是我不能控制 FIQ 中断、这些中断用于 ESM 高电平错误和一个 VIM 中被保留的中断。 两者都是我无法控制的、因此我不确定如何才能防止它们在严重的错误情况下触发。

是否有任何禁用 FIQ 的权变措施? 谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好!

我想知道是否能完全禁用 Hercules 上的所有中断、包括 FIQ。

根据 spna218部分2.5、一旦启用、FIQ 便无法禁用。 但是、我们需要一个完全不能中断的严重错误处理程序。

我 已经使用 CPSID AIF 指令禁用其它中断、但是我不能控制 FIQ 中断、这些中断用于 ESM 高电平错误和一个 VIM 中被保留的中断。 两者都是我无法控制的、因此我不确定如何才能防止它们在严重的错误情况下触发。

是否有任何禁用 FIQ 的权变措施? 谢谢

您好、Robin、

您可以通过设置 CPSR 在特权模式下禁用 IRQ/FIQ 异常。 将 I 位和 F 位更改成了 B1。 _disable_interrupts ()用于设置 CPSR 中的 I 和 F 位,而 _enable_interrupts () 用于清除这两个位(I 和 F)。

有关更多详细信息、请参阅以下主题:

(+) TMS570LS1224:禁用 IRQ 处理程序中的中断会返回无效地址-基于 Arm 的微控制器论坛-基于 Arm 的微控制器- TI E2E 支持论坛

--

谢谢。此致、

Jagadish。

Jagadish、您好!

我 已经使用 CPSID AIF 指令禁用其他中断,但我无法控制 FIQ 中断,

我已经尝试在特权模式中设置这些位。 我 直接尝试了_disable_interrupts ()函数和 CPSID asm 运算。

有多个来源记录 FIQ 的 NMI 行为:

https://e2e.ti.com/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/140945/fiq-disabling

https://e2e.ti.com/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1160270/tms570lc4357-using-arm-effectively/4363117?tisearch=e2e-sitesearch&keymatch=disable%2525252520fiq#4363117

https://www.ti.com/lit/an/spna218/spna218.pdf (第2.5节)

我正在为此行为寻找权变措施。

谢谢。

罗宾

您好、Robin、

在对旧线程进行研究后、我发现了以下内容:

在 Cortex-R4F 中、FIQ 是一个不可屏蔽中断、因此无法 禁用。

复位后、IRQ 和 FIQ 均被禁用(CPSR 中的 I 和 F 位被设定)。 启用 FIQ 后(清除 CPSR 中的 F 位)、便无法再禁用它。

我正在寻找此行为的解决方法。

因此、除了复位后不启用之外、没有其他方法可以禁用 FIQ。 因此、请勿使用中断启用 FIQ 中断至任何其他中断、仅在应用程序中使用 IRQ 中断。

--

谢谢。此致、

Jagadish。

Jagadish、您好!

感谢您帮助我确认这一点。 遗憾的是、没有办法不启用 FIQ 中断、因为 ESM 处理程序之类的东西都需要它们。

但是、我做了一些测试、想看看您是否可以确认行为。 我尝试了以下代码来阻止中断、只要我能告诉它就可以阻止 FIQ 中断。

/* Disable interrupts. FIQ interrupts are unmaskable (spna218 Section 2.5)*/

_disable_interrupt_();

/* Change to FIQ mode to try and prevent FIQ interrupts. Best effort. */

__asm(" MRS R0, CPSR"); /* Load the Current Program Status Register. */

__asm(" BIC R0, R0, #0x1F"); /* Clear the Mode bits [4:0]. */

__asm(" ORR R0, R0, #0x11"); /* Set the Mode to FIQ Mode (b10001). */

__asm(" MSR CPSR, R0"); /* Save changes to CPSR. */

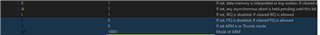

查看 CPSR 时、我可以看到 FIQ 模式已设置、但 F 位保持未设置、这意味着在理论上应该发生中断:

我担心、当我浏览 ARM 文档(https://developer.arm.com/documentation/den0042/a/Exceptions-and-Interrupts/Exception-priorities/Exception-mode-summary)时 、它声称 FIQ 模式应该会屏蔽此位:

这由一个自然 FIQ 手动重构位来进一步支持:

似乎我的"变通办法"不能正确地做到这一点,但我仍然看到屏蔽行为。 您能帮助我确定我是否做了一些仅为未定义行为的行为、或者这是我们的预期吗? 谢谢你。

或者、是否有方法可以配置软件控制的 FIQ?

您好、Robin、

刚才、我通过将 RTI compare_0中断配置为 FIQ 中断来测试您的代码。

e2e.ti.com/.../FIQ_5F00_Disable_5F00_Test.zip

即使在使用代码后、它也不会禁用 FIQ 中断、LED 仍在闪烁。

我的观察结果是:

在 CPSR 中手动设置为 F 位(禁用)不会影响位状态、该位仅在 FIQ 处理程序中自动设置、如下所示。

启用 FIQ 后、禁用 FIQ 的唯一方法仅通过复位。

--

谢谢。此致、

Jagadish。