您好!

我曾 尝试:

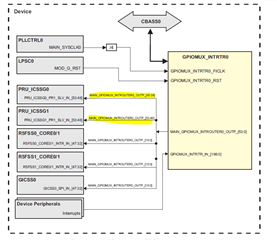

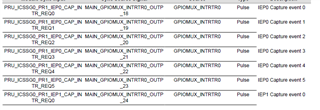

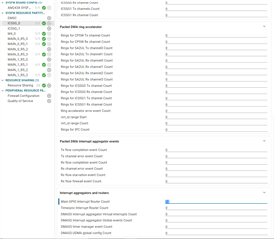

路由 GPIO1_0中断-> MAIN_GPIOMUX_INTROUTER0_OUTP_18

MAIN_GPIOMUX_INTROUTER0_OUTP_18 -> IEP_CAP

和类似地、将 GPIO1_1和 GPIO1_2中断 分别添加到 MAIN_GPIOMUX_INTROUTER0_OUTP_19和 MAIN_GPIOMUX_INTROUTER0_OUTP_20

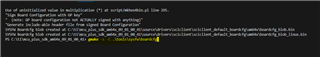

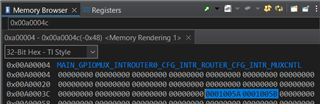

写入 PRU 代码、但它无法正常工作。 然后、我意识到 必须 通过 SCI 客户端修改 GPIOMUX_INTRTR0_MUXCNTL_n。

因此、我在同一 PRU 代码中具有 pinmux、中断和 IEP 设置、并尝试在空 ARM 项目中配置中断路由器。

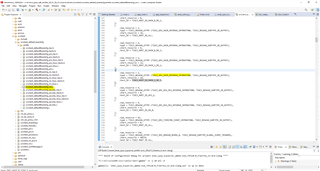

下面是我的 ARM 代码、

main.c

#包含

#包含

#包含

#包含

#define TISCI_DEV_GPIO1 78U

#define TISCI_BANK_SRC_IDX_BASE_GPIO1 (90U)

#define TISCI_DEV_PRU_ICSSG0 81U

int main (空)

{

int32_t 返回值;

结构 tisci_msg_rm_irrq_set_req rmIrqReq;

结构 tisci_msg_rm_irrq_set_resp rmIrqResp;

rmIrqREQ.value_params = 0u;

rmIrqREQ.VALID_PARAMS |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqREQ.VALID_PARAMS |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqREQ.global_event = 0U;

rmIrqREQ.src_id = TISCI_DEV_GPIO1;

rmIrqREQ.src_index = TISCI_BANK_SRC_IDX_BASE_GPIO1 +(((uint32_t) 0)>> 4U);

rmIrqREQ.dst_id = TISCI_DEV_PRU_ICSSG0;

rmIrqREQ.DST_HOST_IRQ = CSLR_PRU_ICSSG0_PR1_IEP0_CAP_INTR_REQ_MAIN_GPIOMUX_INTROUTER0_OUTP_18;

rmIrqReq.ia_id = 0u;

rmIrqReq.vint = 0u;

rmIrqREQ.vint_status_bit_index = 0u;

rmIrqReq.secondary_host = TISCI_MSG_value_rm_unused_secondary_host;

RetVal = Sciclient_rmIrqSet (&rmIrqReq、&rmIrqResp、SystemP_WAIT_FOREVER);

返回0;

}

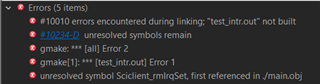

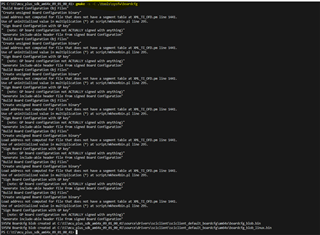

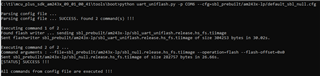

编译上述代码时、它显示5个错误。 请参阅附件。

请帮助我解决错误、我的方法是否正确?

此致。