Other Parts Discussed in Thread: TMS570LS3137

工具与软件:

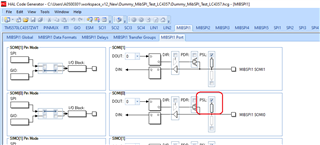

大家好、我正在将 TMS570LS3137 MIBSPI5用作从器件。 我们将 在一个传输组(单芯片选择生效)帧中传输7个16位字。

每个 SPI 传输 从器件 发送7 16位从器件状态并且接收来自主器件的7 16位新命令。

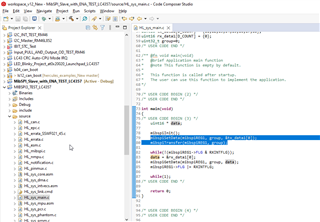

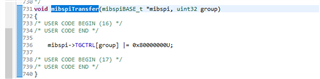

主器件控制 SPI 事务的时序, 事务与从器件异步,使用 mibspiSetData()定期更新 TXRAM 缓冲区。

我们担心、当主器件在从器件更新 TXRAM 缓冲区中的7个数据字的过程中发送 SPI 事务时会发生什么情况。

我们担心前3个16位字可能会从从机发送到主机、然后从机状态数据会更新、帧的后4个字可能与从机状态发送数据的前3个字不一致。

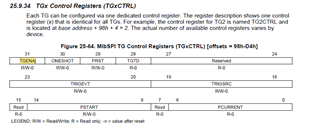

虽然似乎每个16位字都被 单次移动到 TX 移位寄存器(根据《TMS570LS31x/21x 16/32位 RISC 闪存微控制器技术参考手册》的第25.2.2.1节、见下文)、我们如何确保我们的7个16位从传输组作为一个相干数据块进行传输?

谢谢。

-乔

___________________

25.2.2.1写入 SPIDAT0或 SPIDAT1时的数据时序

•如果 TX 移位寄存器和 TXBUF 都为空、那么数据就直接被复制到 TX 移位寄存器中

寄存器。 对于带有 DMA 的器件、如果 DMA 被启用、一个发送 DMA 请求(TX_DMA_REQ)被

生成以导致提取下一个字。 如果使能了发送中断、则表明发送器已空

中断被生成。

•如果 TX 移位寄存器已满或处于移位过程中并且如果 TXBUF 已过期、则数据将

写入 SPIDAT0/SPIDAT1被复制到 TXBUF、TXFULL 标志同时设置为1。

•当一个移位操作完成时、来自 TXBUF 的数据(如果已满)被复制到 TX 移位寄存器中

TXFULL 标志清零、以指示可以提取下一个数据。 发送 DMA 请求

(如果使能)或发送器空中断(如果使能)将同时产生。